在最后一章里,我们来做几个实战项目,一方面是对前面学习知识的一种回顾,另一方面这几个小项目也非常贴近实际工程,其中例程“SD卡存放音频WAV播放”比较偏向校园电子大赛项目,比较新颖涉及知识点多,会给面试官们留下不错的印象;例程“OV7725摄像头实时采集HDMI显示边缘检测”,帮助大家举一反三地实现其他图像前后处理、多帧缓存技术等应用; 例程“USB2.0/RS232/LAN控制并行DAC输出任意频率的正弦波、梯形波、三角波、方波“,有很多关键技术,涵盖报文分割、报文解析、串口Modbus CRC校验、USB2.0 CRC校验、网口ARP/ ICMP/ UDP协议实现,DDS IP核等。

在这一个例程“SD卡存放音频WAV播放”和最后一个例程“USB2.0/RS232/LAN控制并行DAC输出任意频率正弦波、梯形波、三角波、方波”中,其实都涉及到DAC数模转换的实际应用。

在这里大家不妨想想DAC数模转换和ADC模数转换的应用场景,相信本科学自动化、电子、通信等专业的同学,上学时都会开设“数字信号处理”、“自动化控制原理”、“信号与系统”、“电力电子”、“模拟电路”等相关课程,当时只记得书上各种各样的复杂公式推导和抽象概念理论,仅仅看书通过字面意思学来学去,还是感到不知所云。

有趣的是在工作以后再遇到这些问题时,迫不得已笔者试着买了几本国外的教程学习,不得不说国外教程写得真的很好站在了实践的角度在写书,而相反的国内教程把公式和理论无限放大内容枯燥,在这推荐一本数字信号处理好书给大家“understanding digital signal procesing 2nd edition”,书里深入浅出地把数字信号处理中的滤波器设计、采样和量化、离散傅立叶变换、数字变频等说得很清楚,这本书的中文电子版后期会给出百度网盘下载链接。

在这个例程中我们通过一颗应用广泛的音频编解码芯片WM8731去播放SD卡中存储的WAV格式语音数据文件,这也是一个比较综合性的项目类例程,如图1所示是豌豆开发板Artix7上WM8731电路。

图1 豌豆开发板Artix7上WM8731电路

WM8731芯片本身既支持通过DAC数模转换接口把语音数据转化为音频信号通过输出端音频连接器外放,也支持ADC模数转换接口把输入端音频连接器上的音频信号采集为语音数据,对照原理图和实物大家可以清楚地看到豌豆开发板上板载3个音频连接器,其中粉色的接口作为麦克风输入,绿色的接口作为耳机输出,蓝色的接口作为音频输入用于连接DVD等音频输出口。

在这个例程中我们仅使用了WM8731的DAC转换功能,即把SD卡中事先存储的WAV格式语音数据转化为音频信号通过输出端绿色接口的音频连接器外放,大家不妨把这个例程当做一个实战小项目,同样的在编码之前我们来一起读一读WM8731的芯片手册,下面请朋友们跟随笔者的脚步,化难为易,化整为零从64页繁琐的手册中整理出程序设计方面关键性信息。

如图2所示是WM8731的功能概述和典型应用,大家可以清楚地看到WM8731是一款高效的耳机驱动芯片,其中给出了一些关键性的规格指标,包括了SNR信噪比参数、模数和数模转换的电压范围和采样频率、主从模式配置、芯片封装类型等,广泛应用在MP3、多功能耳机、录音机等产品上。

图2 WM8731的功能概述和典型应用

如图3所示是WM8731的内部结构和引脚说明这里可以对照图1中所示的原理图,其中关键的部分笔者都用了红框进行标记,对于本例程的功能实现,实际上我们关心的只需要去关注3个部分即可,即结构图中的1处的初始化配置控制接口,2处的语音数据到音频信号数模DAC转换接口,3处的音频连接器耳机输出接口,分别对应引脚图中6处的CSB、MODE、SCLK、SDIN,4处的BCLK、DACDAT、DACLRC、ADCDAT、ADCLRC以及5处的LHPOUT和RHPOUT。

图3 WM8731的内部结构和引脚说明

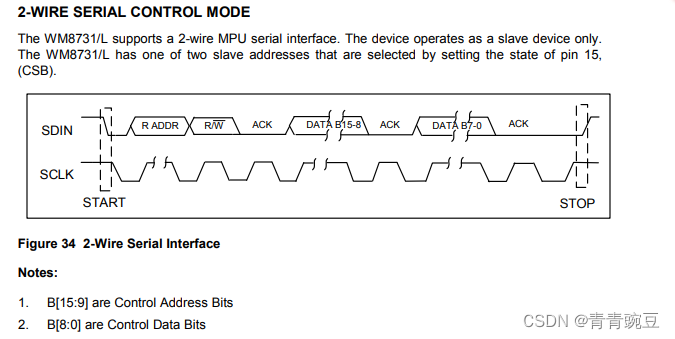

对照上述3个关键点,我们再去带着问题在手册中寻找关键的信息,首先第一点初始化模式配置上,细心的同学不难发现图7-3中包含了4个相关引脚即CSB、MODE、SCLK、SDIN,注意到手册里指出WM8731初始化配置中支持三线制和二线制两种模式。

如图4所示是WM8731的三线制和二线制配置时序逻辑示意图,大家可以看出在PCB设计上只需要把MODE引脚下拉到地接低电平即默认为二线制配置方式,而把MODE引脚上拉到电源接高电平即默认为三线制配置方式,三线制的通信模式类似SPI通信,二线制的通信模式则类似IIC通信,为了节约豌豆开发板的引脚,在硬件设计上选择了二线制通信方式,即把MODE引脚接地为低电平,同时不难看出CSB引脚在二线制的通信模式下不起任何作用,接地或者不接都可以。

图4 WM8731的三线制和二线制配置时序逻辑示意图

其次我们需要去关注5个核心引脚即BCLK、DACDAT、DACLRC、ADCDAT、ADCLRC,注意到如上图2的芯片概述所示,WM8731芯片内部ADC和DAC的采样频率是8KHz到96KHz可调的,同时对应的可转换数据长度也是16-32位可调的。

再次芯片又有I2S、Left justified、Right justified、DSP/PCM四种数字音频接口模式和主从时钟模式可供用户选择,并且这些模式的配置都是通过WM8731芯片内部11个寄存器初始化而来的。

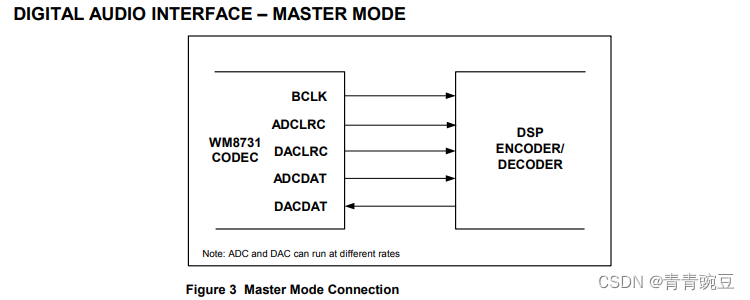

在分析完这些关键信息后,我们再带着问题到数据手册里去逐一寻找答案,如图5所示是WM8731在主从时钟模式下的接口连接示意图,注意到在主时钟模式下BCLK(数字音频的位时钟)、ADCLRC(ADC数字音频信号输出)、DACLRC(DAC采样左/右声道信号)都是由WM8731端产生给到SOC芯片,而相反的在从时钟模式下这三个信号都由SOC芯片产生去给到WM8731端,所以为了简化设计,我们可以选择配置成主时钟模式,由WM8731端去产生BCLK、ADCLRC、DACLRC三个信号,而FPGA端则用一个快时钟去实时检测这些信号的上升沿或者下降沿,再去进一步地实现采集数据或者发送数据等处理。

图5 WM8731在主从时钟模式下的接口连接示意图

如图6所示是WM8731在四种数字音频接口模式下的说明,结合手册里的这段核心说明来为大家简要地去解读BCLK、DACDAT、DACLRC、ADCDAT、ADCLRC这5个引脚的作用。

首先WM8731芯片支持四种数字音频接口模式即I2S、Left justified、Right justified、DSP/PCM,其对应的时序逻辑会马上逐一展开介绍。

其次对于ADC的采样,注意到手册上的描述:数字音频接口从内部ADC数字滤波器获取数据并将其置于ADCDAT引脚上输出,所以ADCDAT上产生的是左声道和右声道复用在一起的数字音频数据流,ADCLRC则是控制ADCDAT上是否存在左声道或右声道数据,并且ADCDAT上产生的数据流与BCLK时钟同步。

简而言之即ADCDAT引脚上采集了音频接口输入端产生的模拟信号并把其转换为音频数据流,ADCLRC在不同模式下控制了ADCDAT上产生的是左声道和右声道数据流,BCLK则作为同步时钟同步了ADCDAT引脚上的输出数据。

再次对于DAC的变换,和ADC的采样大同小异,数字音频接口还接收内部DAC数字滤波器的数字音频数据,也是左声道和右声道复用在一起的数字音频数据流,同样的也需要DACLRC指示左声道和右声道,以及BCLK时钟同步DACDAT上的输入数据,将其通过音频接口输出端外放。

最后我们还需要注意到一点即四种模式下都是MSB即高比特位先操作,且一次操作数据位是16-32位。

图6 WM8731在四种数字音频接口模式下的说明

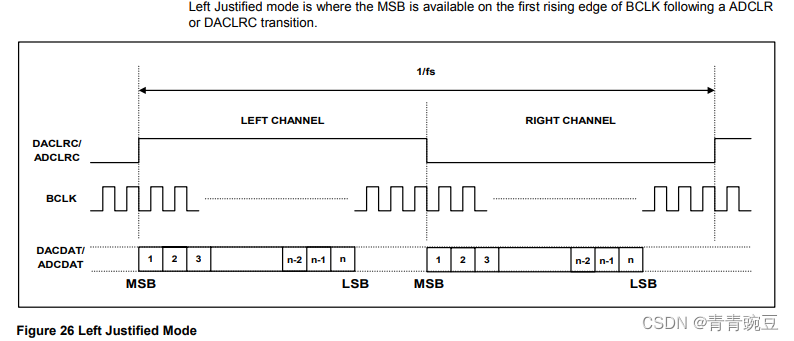

如图7所示是WM8731在Left justified模式下的时序逻辑图,可以看到手册上对于该模式的描述为:Left Justified mode is where the MSB is available on the first rising edge of BCLK following a ADCLRC or DACLRC transition,对照图片和描述很容易理解到,即在Left justified模式下,ADCLRC或者DACLRC传输数据的最高位在BCLK第一个上升沿有效,且ADCLRC或者DACLRC为高电平时代表左声道,为低电平时代表右声道。

图7 WM8731在Left justified 模式下的时序逻辑图

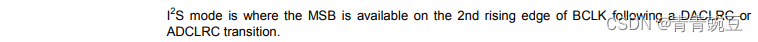

如图8所示是WM8731在I2S模式下的时序逻辑图,可以看到手册上对于该模式的描述为:I2S mode is where the MSB is available on the 2nd rising edge of BCLK following a DACLRC or ADCLRC transition,对照图片和描述很容易理解到,即在I2S模式下,ADCLRC或者DACLRC传输数据的最高位在BCLK第二个上升沿有效,且ADCLRC或者DACLRC为高电平时代表右声道,为低电平时代表左声道。

图8 WM8731在I2S模式下的时序逻辑图

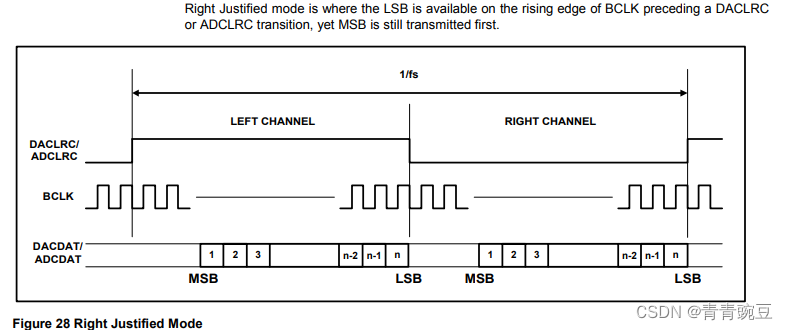

如图9所示是WM8731在Right justified模式下的时序逻辑图,可以看到手册上对于该模式的描述为:Right Justified mode is where the LSB is available on the rising edge of BCLK preceding a DACLRC or ADCLRC transition, yet MSB is still transmitted first,对照图片和描述很容易理解到,即在Right justified模式下,ADCLRC或者DACLRC传输数据的最低位在BCLK上升沿可用,同样也是最高位先被发送,且ADCLRC或者DACLRC为高电平时代表左声道,为低电平时代表右声道。

图9 WM8731在Right justified模式下的时序逻辑图

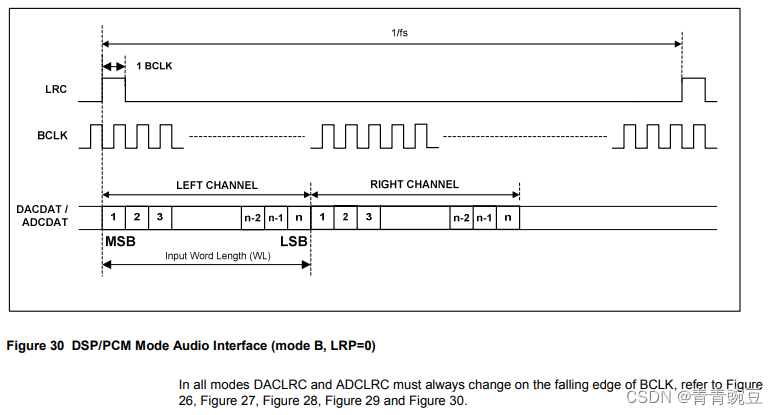

如图10所示是WM8731在DSP/PCM模式下的时序逻辑图,可以看到手册上对于该模式的描述为:In DSP/PCM mode, the left channel MSB is available on either the 1st (mode B) or 2nd (mode A) rising edge of BCLK (selectable by LRP) following a rising edge of LRC. Right channel data immediately follows left channel data. Depending on word length, BCLK frequency and sample rate, there may be unused BCLK cycles between the LSB of the right channel data and the next sample,对照图片和描述很容易理解到,即在DSP/PCM模式下,又细分为A和B两种模式,这种模式相对于前三种模式更加灵活,操作数字音频接口可方便地支持不同的采样率和字长,也就是说根据字长、BCLK频率时钟以及所配置的采样率,右通道数据的最低位和下一个采样之间可能存在多个没有使用到的BCLK周期。

同时应该注意到图10的手册下方的标注:In all modes DACLRC and ADCLRC must always change on the falling edge of BCLK, refer to Figure 26, Figure 27, Figure 28, Figure 29 and Figure 30,即在所有的模式下DACLRC和ADCLRC必须始终在BCLK下降沿变化,这也是后续程序设计中的一项参考点。

图10 WM8731在DSP/PCM模式下的时序逻辑图

我正在使用i18n从头开始构建一个多语言网络应用程序,虽然我自己可以处理一大堆yml文件,但我说的语言(非常)有限,最终我想寻求外部帮助帮助。我想知道这里是否有人在使用UI插件/gem(与django上的django-rosetta不同)来处理多个翻译器,其中一些翻译器不愿意或无法处理存储库中的100多个文件,处理语言数据。谢谢&问候,安德拉斯(如果您已经在rubyonrails-talk上遇到了这个问题,我们深表歉意) 最佳答案 有一个rails3branchofthetolkgem在github上。您可以通过在Gemfi

我看到这个错误:translationmissing:da.datetime.distance_in_words.about_x_hours我的语言环境文件:http://pastie.org/2944890我的看法:我已将其添加到我的application.rb中:config.i18n.load_path+=Dir[Rails.root.join('my','locales','*.{rb,yml}').to_s]config.i18n.default_locale=:da如果我删除I18配置,帮助程序会处理英语。更新:我在config/enviorments/devolpment

如果我使用ruby版本2.5.1和Rails版本2.3.18会怎样?我有基于rails2.3.18和ruby1.9.2p320构建的rails应用程序,我只想升级ruby的版本,而不是rails,这可能吗?我必须面对哪些挑战? 最佳答案 GitHub维护apublicfork它有针对旧Rails版本的分支,有各种变化,它们一直在运行。有一段时间,他们在较新的Ruby版本上运行较旧的Rails版本,而不是最初支持的版本,因此您可能会发现一些关于需要向后移植的有用提示。不过,他们现在已经有几年没有使用2.3了,所以充其量只能让更

大家好!我对我的:username字段进行了一个小的验证,它应该是4到30个字符。我写了一个验证::length=>{:within=>4..30,:message=>I18n.t('activerecord.errors.range')-我想显示一个错误各种错误的消息(不像,太长或太短),但这里有一个问题-我可以将最小值和最大值都传递给翻译,以便有类似的东西:用户名应该在4到30个字符之间。目前我有:range:"shouldbebetween%{count}and%{count}characters",这显然不起作用(只是为了检查)。是否可以从范围中获取这些值?谢谢大家的指教!

需求:要创建虚拟机,就需要给他提供一个虚拟的磁盘,我们就在/opt目录下创建一个10G大小的raw格式的虚拟磁盘CentOS-7-x86_64.raw命令格式:qemu-imgcreate-f磁盘格式磁盘名称磁盘大小qemu-imgcreate-f磁盘格式-o?1.创建磁盘qemu-imgcreate-fraw/opt/CentOS-7-x86_64.raw10G执行效果#ls/opt/CentOS-7-x86_64.raw2.安装虚拟机使用virt-install命令,基于我们提供的系统镜像和虚拟磁盘来创建一个虚拟机,另外在创建虚拟机之前,提前打开vnc客户端,在创建虚拟机的时候,通过vnc

如果特定语言环境中缺少翻译,如何配置i18n以使用en语言环境翻译?当前已插入翻译缺失消息。我正在使用RoR3.1。 最佳答案 找到相似的question这里是答案:#application.rb#railswillfallbacktoconfig.i18n.default_localetranslationconfig.i18n.fallbacks=true#railswillfallbacktoen,nomatterwhatissetasconfig.i18n.default_localeconfig.i18n.fallback

我正在使用Enumerizegemhttps://github.com/brainspec/enumerize/它允许我以简单的形式使用漂亮的选择。并且此选择中的所有选项均已翻译。en:enumerize:user:sex:male:'Man'female:'Woman'所以,在我的表单中,我选择了变体“男人”和“女人”。当我用“男人”值保存记录时,我得到了“男性”值的性别属性。现在我想在显示页面上将该值显示为“Man”,但是=@user.sex输出为'male'而不是'Man' 最佳答案 我可能会使用.text方法(您可以通过使用

我一直在寻找一种以编程方式或通过命令行将mp3转换为aac的方法,但没有成功。理想情况下,我有一段代码可以从我的Rails应用程序中调用,将mp3转换为aac。我安装了ffmpeg和libfaac,并能够使用以下命令创建aac文件:ffmpeg-itest.mp3-acodeclibfaac-ab163840dest.aac当我将输出文件的名称更改为dest.m4a时,它无法在iTunes中播放。谢谢! 最佳答案 FFmpeg提供AAC编码功能(如果您已编译它们)。如果您使用的是Windows,则可以从here获取完整的二进制文件。

当音乐碰上区块链技术,会擦出怎样的火花?或许周杰伦已经给了我们答案。8月29日下午,B站独家首发周杰伦限定珍藏Demo独家访谈VCR,周杰伦在VCR里分享了《晴天》《青花瓷》《搁浅》《爱在西元前》四首经典歌曲Demo背后的创作故事,并首次公布18年前未发布的神秘作品《纽约地铁》的Demo。在VCR中,方文山和杰威尔音乐提及到“多亏了区块链技术,现在我们可以将这些Demos,变成独一无二具有收藏价值的艺术品,这些Demos可以在薄盒(国内数藏平台)上听到。”如何将音乐与区块链技术相结合,薄盒方面称:“薄盒作为区块链技术服务方,打破传统对于区块链技术只能作为数字收藏的理解。聚焦于区块链技术赋能,在

提供3种Ubuntu系统安装微信的方法,在Ubuntu20.04上验证都ok。1.WineHQ7.0安装微信:ubuntu20.04安装最新版微信--可以支持微信最新版,但是适配的不是特别好;比如WeChartOCR.exe报错。2.原生微信安装:linux系统下的微信安装(ubuntu20.04)--微信适配的最好,反应最快,但是微信版本只到2.1.1,版本太老,很多功能都没有。3.深度deepin-wine6安装微信:ubuntu20.04+系统deepin-wine6安装新版微信--综合比较好,当前个人使用此种方法1个月,微信版本3.4;没什么大问题,尚可。一、WineHQ7.0安装微信