文章目录

5、使用ISE软件完成组合逻辑设计的输入并仿真

6、掌握Testbech中组合逻辑测试文件的写法

7、下载并测试实现的逻辑功能

module m4_1(in0,in1,in2,in3,S,F);

input in0,in1,in2,in3;

input [1:0]S; //定义输入

output reg F; //定义输出,F定义为reg型

always @* //敏感词使用*

begin

case(S) //case语句实现选择输出

2'b00:F<=in0;

2'b01:F<=in1;

2'b10:F<=in2;

2'b11:F<=in3; //实现输入S=00、01、10、11时,输出 in0,in1,in2,in3

endcase

end

endmodule

`timescale 1ns / 1ps

module m4_1_tb;

reg in0,in1,in2,in3;

reg [1:0] S;

wire F;

m4_1 uut (

.in0(in0),

.in1(in1),

.in2(in2),

.in3(in3),

.S(S),

.F(F)

); //例化模块

initial begin

in0=0;

in1=0;

in2=0;

in3=0;

S = 0; //初始化输入

#100;

fork //fork-join实现并行输入

repeat(5) #400 S=S+1; //每400ns S+1

repeat(100) #20 in0=~in0;

repeat(50) #40 in1=~in1;

repeat(25) #80 in2=~in2;

repeat(10) #200 in3=~in3; //输入in0,in1,in2,in3信号为不 同的脉冲信号,方便选择后观察

join

end

endmodule

module d3_8(D,Y);

input [2:0]D; //定义三位输入

output reg[7:0]Y; //定义八位输出

always@(D) //使用always块,敏感词选用D

begin

case(D) //case语句实现3-8过程

3'b000:Y=8'b1111_1110;

3'b001:Y=8'b1111_1101;

3'b010:Y=8'b1111_1011;

3'b011:Y=8'b1111_0111;

3'b100:Y=8'b1110_1111;

3'b101:Y=8'b1101_1111;

3'b110:Y=8'b1011_1111;

3'b111:Y=8'b0111_1111; //输入和输出一一选择对应

endcase

end

endmodule

`timescale 1ns / 1ps

module d3_8_tb;

reg [2:0] D;

wire [7:0] Y;

d3_8 uut (

.D(D),

.Y(Y)

);

initial begin

D = 0;

#100; //进行输入端口初始化

repeat(10) //重复十次

begin

D=3'b000;

#20;

D=3'b001;

#20;

D=3'b010;

#20;

D=3'b011;

#20;

D=3'b100;

#20;

D=3'b101;

#20;

D=3'b110;

#20;

D=3'b111;

#20; //依次使D等于0-7,观察输出

end

end

endmodule

module en8_3(en,I,Y,Yx,Yn);

input en;

input [7:0]I;

output reg[2:0]Y;

output reg Yx,Yn;

always@(I)

begin

if(!en)

begin

Y=3'b111;

Yx=1;

Yn=1;

end

else

begin

if(I==8'b1111_1111)

begin

Y=3'b111;

Yx=1;

Yn=0;

end

else

begin

Yx=0;

Yn=1;

if(I[7]==0)

Y=3'b000;

else if(I[6]==0)

Y=3'b001;

else if(I[5]==0)

Y=3'b010;

else if(I[4]==0)

Y=3'b011;

else if(I[3]==0)

Y=3'b100;

else if(I[2]==0)

Y=3'b101;

else if(I[1]==0)

Y=3'b110;

else if(I[0]==0)

Y=3'b111;

end

end

end

endmodule

`timescale 1ns / 1ps

module en8_3_tb;

reg en;

reg [7:0] I;

wire [2:0] Y;

wire Yx;

wire Yn;

en8_3 uut (

.en(en),

.I(I),

.Y(Y),

.Yx(Yx),

.Yn(Yn)

);

initial begin

en = 0;

I = 0;

#100;

en=1;

repeat(20)

begin

I=8'b1111_1111;

#20;

I=8'b0111_1111;

#20;

I=8'b1011_1111;

#20;

I=8'b1101_1111;

#20;

I=8'b1110_1111;

#20;

I=8'b1111_0111;

#20;

I=8'b1111_1011;

#20;

I=8'b1111_1101;

#20;

I=8'b1111_1110;

#20;

end

end

endmodule

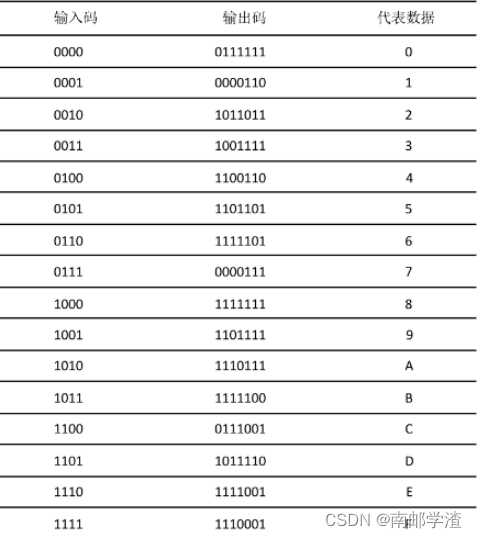

module led7(D,Y,en);

input [3:0]D;

input en;

output reg[6:0]Y;

always@(D)

begin

if(!en)

Y=7'b000_0000;

else

case(D)

4'b0000:Y=7'b011_1111;

4'b0001:Y=7'b000_0110;

4'b0010:Y=7'b101_1011;

4'b0011:Y=7'b100_1111;

4'b0100:Y=7'b110_0110;

4'b0101:Y=7'b110_1101;

4'b0110:Y=7'b111_1101;

4'b0111:Y=7'b000_0111;

4'b1000:Y=7'b111_1111;

4'b1001:Y=7'b110_1111;

4'b1010:Y=7'b111_0111;

4'b1011:Y=7'b111_1100;

4'b1100:Y=7'b011_1001;

4'b1101:Y=7'b101_1110;

4'b1110:Y=7'b111_1001;

4'b1111:Y=7'b111_0001;

endcase

end

endmodule

`timescale 1ns / 1ps

module led7_tb;

reg [3:0] D;

reg en;

wire [6:0] Y;

led7 uut (

.D(D),

.Y(Y),

.en(en)

);

initial begin

D = 0;

en = 0;

#100;

en=1;

repeat(10)

begin

D=4'b0000;

#20;

D=4'b0001;

#20;

D=4'b0010;

#20;

D=4'b0011;

#20;

D=4'b0100;

#20;

D=4'b0101;

#20;

D=4'b0110;

#20;

D=4'b0111;

#20;

D=4'b1000;

#20;

D=4'b1001;

#20;

D=4'b1010;

#20;

D=4'b1011;

#20;

D=4'b1100;

#20;

D=4'b1101;

#20;

D=4'b1110;

#20;

D=4'b1111;

#20;

end

end

endmodule

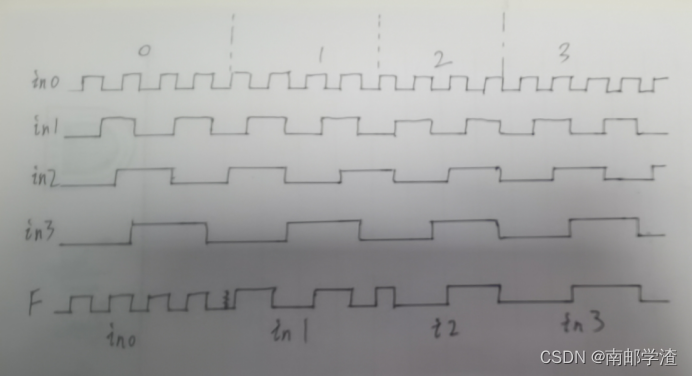

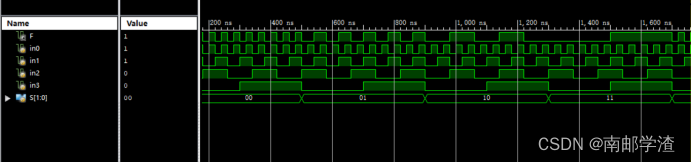

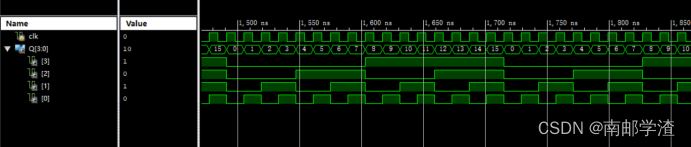

1、四选一数据选择器波形图:

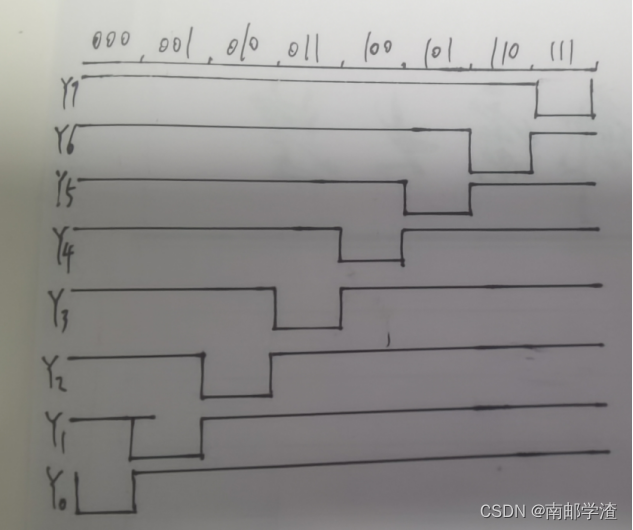

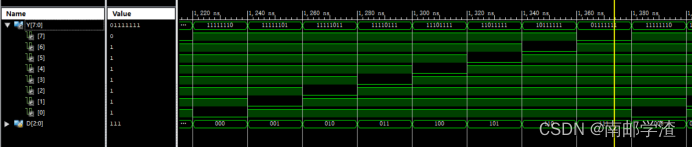

2、3-8译码器波形图:

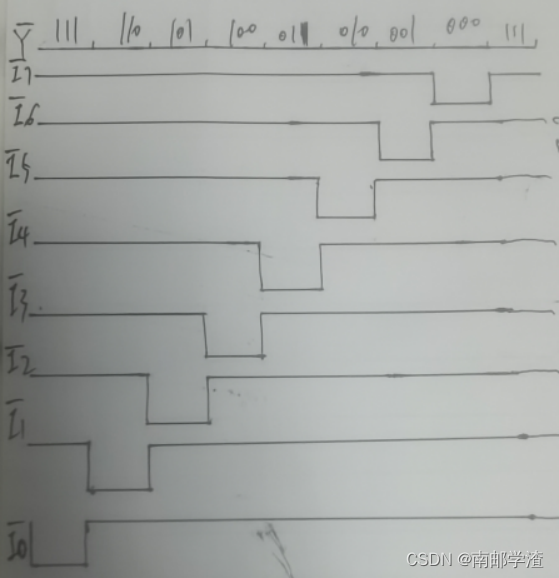

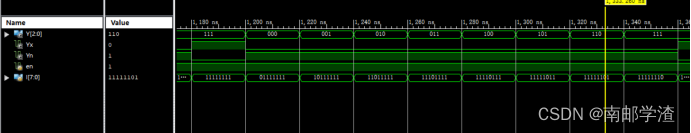

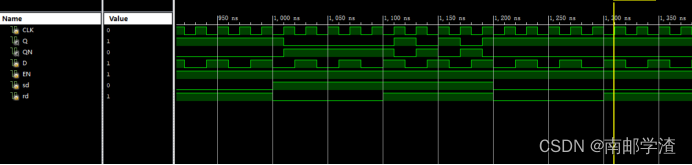

3、8-3优先编码器波形图:

1、四选一数据选择器仿真图:

2、3-8译码器仿真图:

3、8-3优先编码器仿真图:

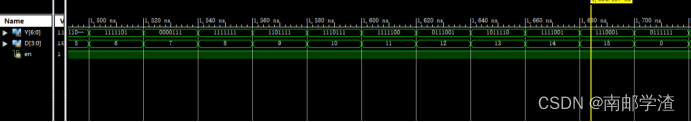

4、十六进制7段led显示译码器:

1、使用ISE软件完成时序逻辑电路的设计输入并仿真

2、掌握tb中时序逻辑测试文件的写法

3、下载并测试实现的逻辑电路

module and74161(CR,ld,P,T,clk,Q,rst,A,B,C,D);

input CR,ld,P,T,rst;

input clk;

input A,B,C,D;

output reg[3:0]Q;

always @(posedge clk,negedge rst)

begin

if(rst==0)

Q<=4'b0;

else if(CR==0)

Q<=4'b0;

else if(CR&ld==0)

Q<={A,B,C,D};

else if(CR&ld&P&T)

Q<=Q+1;

else if(CR&ld&P==0)

Q<=Q;

else if(CR&ld&T==0)

Q<=Q;

end

endmodule

`timescale 1ns / 1ps

module and74161_tb;

reg CR;

reg ld;

reg P;

reg T;

reg clk;

reg A,B,C,D;

reg rst;

wire [3:0] Q;

and74161 uut (

.CR(CR),

.ld(ld),

.P(P),

.T(T),

.clk(clk),

.Q(Q),

.A(A),

.B(B),

.C(C),

.D(D),

.rst(rst)

);

initial begin

CR = 0;

ld = 0;

P = 0;

T = 0;

clk = 0;

A=0;

B=0;

C=0;

D=0;

rst=0;

#100;

A=0; B=1;C=0;D=1;

rst=1;

CR=1;ld=0;#50; //ABCD

rst=1;

CR=0;ld=1;P=1;T=1;

#20; //清0

rst=1;

CR=1;ld=0;P=0;T=0;

#20; //清0

rst=1;

CR=1;ld=1;P=0;T=1;

#20;

rst=1;

CR=1;ld=1;P=1;T=0;

#20;

rst=1;

CR=1;ld=1;P=1;T=1;

#2000;

end

always #7 clk=~clk;

endmodule

module dff(D,EN,CLK,sd,rd,Q,QN);

input D,EN,CLK,sd,rd;

output reg Q;

output reg QN;

always @(posedge CLK)

begin

if(EN&sd==0)

begin

Q<=1;QN<=0;

end

else if(EN&sd==1&rd==0)

begin

Q<=0;QN<=1;

end

else if(EN&sd==1&rd==1)

begin

Q<=D;QN<=~D;

end

else

begin

Q<=Q;QN<=QN;

end

end

endmodule

`timescale 1ns / 1ps

module dff_tb;

reg D;

reg EN;

reg CLK;

reg sd;

reg rd;

wire Q;

wire QN;

dff uut (

.D(D),

.EN(EN),

.CLK(CLK),

.sd(sd),

.rd(rd),

.Q(Q),

.QN(QN)

);

initial begin

D = 0;

EN = 0;

CLK = 0;

sd = 0;

rd = 0;

#100;

EN=1;

end

initial

fork

forever #100 rd=rd+1;

forever #200 sd=sd+1;

forever #20 D=D+1;

join

always #10 CLK=~CLK; //输入时钟

endmodule

module counter5(en,clk,cnt,co,rst_n);

input en;

input clk;

input rst_n;

output reg [3:0]cnt;

output co;

always @(posedge clk,negedge rst_n)

begin

if(!rst_n)

cnt<=4'b0011;

else if(en&cnt==4'b0111)

cnt<=4'b0011;

else if(en)

cnt<=cnt+1'b1;

else

cnt<=cnt;

end

assign co=cnt[0]&cnt[1]&cnt[2];

endmodule

`timescale 1ns / 1ps

module counter5_tb;

reg en;

reg clk;

reg rst_n;

wire [3:0] cnt;

wire co;

counter5 uut (

.en(en),

.clk(clk),

.cnt(cnt),

.co(co),

.rst_n(rst_n)

);

initial begin

en = 0;

clk = 0;

rst_n = 0;

#100;

en=1;

rst_n=1;

end

always #7 clk=~clk;

endmodule

module reg74194(cr,clk,sr,sl,M,Q,D);

input cr,clk,sr,sl;

input [3:0]D;

input [1:0]M;

output reg[3:0]Q;

always @(posedge clk)

begin

if(!cr)

Q<=4'b0000;

else if(cr&M==2'b11)

Q<=D;

else if(cr&M==2'b01)

begin

Q[2:0]<=Q[3:1];

Q[3]<=sr;

end

else if(cr&M==2'b10)

begin

Q[3:1]<=Q[2:0];

Q[0]<=sl;

end

else

Q<=Q;

end

endmodule

`timescale 1ns / 1ps

module reg74194_tb;

reg cr;

reg clk;

reg sr;

reg sl;

reg [1:0] M;

reg [3:0] D;

wire [3:0] Q;

reg74194 uut (

.cr(cr),

.clk(clk),

.sr(sr),

.sl(sl),

.M(M),

.Q(Q),

.D(D)

);

initial begin

cr = 0;

clk = 0;

sr = 0;

sl = 0;

M = 0;

D = 0;

#100;

cr=1;M=2'b11;

D=4'b1011;

#50;

cr=1;M=2'b01;sr=1'b1;

#50;

cr=1;M=2'b01;sr=1'b0;

#50;

cr=1;M=2'b10;sl=1'b1;

#50;

cr=1;M=2'b10;sl=1'b0;

#50;

cr=1;M=2'b00;

#50;

end

always #7 clk=~clk;

endmodule

1、74161仿真波形图:

2、D触发器(异步复位与同步使能、异步置位与异步复位)

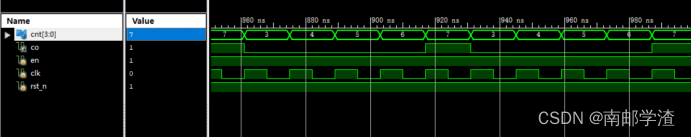

3、模M计数器(实现模5计数器,五个状态为3,4,5,6,7)

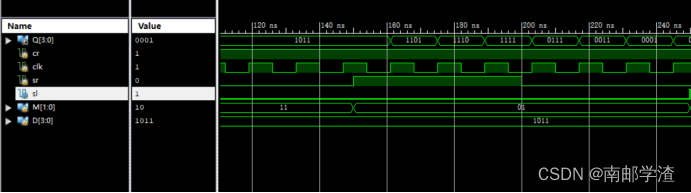

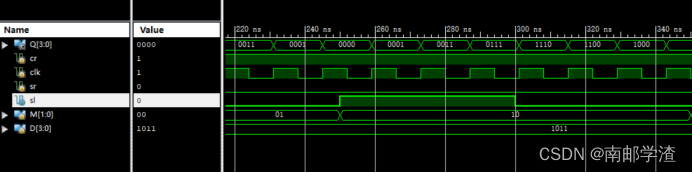

4、移位寄存器74194

左移:

右移:

我正在尝试测试是否存在表单。我是Rails新手。我的new.html.erb_spec.rb文件的内容是:require'spec_helper'describe"messages/new.html.erb"doit"shouldrendertheform"dorender'/messages/new.html.erb'reponse.shouldhave_form_putting_to(@message)with_submit_buttonendendView本身,new.html.erb,有代码:当我运行rspec时,它失败了:1)messages/new.html.erbshou

我在从html页面生成PDF时遇到问题。我正在使用PDFkit。在安装它的过程中,我注意到我需要wkhtmltopdf。所以我也安装了它。我做了PDFkit的文档所说的一切......现在我在尝试加载PDF时遇到了这个错误。这里是错误:commandfailed:"/usr/local/bin/wkhtmltopdf""--margin-right""0.75in""--page-size""Letter""--margin-top""0.75in""--margin-bottom""0.75in""--encoding""UTF-8""--margin-left""0.75in""-

我在我的项目目录中完成了compasscreate.和compassinitrails。几个问题:我已将我的.sass文件放在public/stylesheets中。这是放置它们的正确位置吗?当我运行compasswatch时,它不会自动编译这些.sass文件。我必须手动指定文件:compasswatchpublic/stylesheets/myfile.sass等。如何让它自动运行?文件ie.css、print.css和screen.css已放在stylesheets/compiled。如何在编译后不让它们重新出现的情况下删除它们?我自己编译的.sass文件编译成compiled/t

我有一个对象has_many应呈现为xml的子对象。这不是问题。我的问题是我创建了一个Hash包含此数据,就像解析器需要它一样。但是rails自动将整个文件包含在.........我需要摆脱type="array"和我该如何处理?我没有在文档中找到任何内容。 最佳答案 我遇到了同样的问题;这是我的XML:我在用这个:entries.to_xml将散列数据转换为XML,但这会将条目的数据包装到中所以我修改了:entries.to_xml(root:"Contacts")但这仍然将转换后的XML包装在“联系人”中,将我的XML代码修改为

为了将Cucumber用于命令行脚本,我按照提供的说明安装了arubagem。它在我的Gemfile中,我可以验证是否安装了正确的版本并且我已经包含了require'aruba/cucumber'在'features/env.rb'中为了确保它能正常工作,我写了以下场景:@announceScenario:Testingcucumber/arubaGivenablankslateThentheoutputfrom"ls-la"shouldcontain"drw"假设事情应该失败。它确实失败了,但失败的原因是错误的:@announceScenario:Testingcucumber/ar

我在我的项目中添加了一个系统来重置用户密码并通过电子邮件将密码发送给他,以防他忘记密码。昨天它运行良好(当我实现它时)。当我今天尝试启动服务器时,出现以下错误。=>BootingWEBrick=>Rails3.2.1applicationstartingindevelopmentonhttp://0.0.0.0:3000=>Callwith-dtodetach=>Ctrl-CtoshutdownserverExiting/Users/vinayshenoy/.rvm/gems/ruby-1.9.3-p0/gems/actionmailer-3.2.1/lib/action_mailer

我的瘦服务器配置了nginx,我的ROR应用程序正在它们上运行。在我发布代码更新时运行thinrestart会给我的应用程序带来一些停机时间。我试图弄清楚如何优雅地重启正在运行的Thin实例,但找不到好的解决方案。有没有人能做到这一点? 最佳答案 #Restartjustthethinserverdescribedbythatconfigsudothin-C/etc/thin/mysite.ymlrestartNginx将继续运行并代理请求。如果您将Nginx设置为使用多个上游服务器,例如server{listen80;server

在MRIRuby中我可以这样做:deftransferinternal_server=self.init_serverpid=forkdointernal_server.runend#Maketheserverprocessrunindependently.Process.detach(pid)internal_client=self.init_client#Dootherstuffwithconnectingtointernal_server...internal_client.post('somedata')ensure#KillserverProcess.kill('KILL',

我已经从我的命令行中获得了一切,所以我可以运行rubymyfile并且它可以正常工作。但是当我尝试从sublime中运行它时,我得到了undefinedmethod`require_relative'formain:Object有人知道我的sublime设置中缺少什么吗?我正在使用OSX并安装了rvm。 最佳答案 或者,您可以只使用“require”,它应该可以正常工作。我认为“require_relative”仅适用于ruby1.9+ 关于ruby-主要:Objectwhenrun

我花了三天的时间用头撞墙,试图弄清楚为什么简单的“rake”不能通过我的规范文件。如果您遇到这种情况:任何文件夹路径中都不要有空格!。严重地。事实上,从现在开始,您命名的任何内容都没有空格。这是我的控制台输出:(在/Users/*****/Desktop/LearningRuby/learn_ruby)$rake/Users/*******/Desktop/LearningRuby/learn_ruby/00_hello/hello_spec.rb:116:in`require':cannotloadsuchfile--hello(LoadError) 最佳