全系列:《基于Xilinx的时序分析、约束和收敛》目录与传送门

下图是一张典型的FPGA与上游器件、下游器件通信的示意图:

其可以划分为4条基本的数据路径,这4条路径也是需要进行时序约束的最基本路径。

(1)寄存器到寄存器

路径2,FPGA内部的寄存器到另一个寄存器, 即reg2reg(寄存器到寄存器),需要对其进行约束以满足FPGA端寄存器的建立时间和保持时间要求。

路径2约束的是FPGA内部源寄存器(起点)和FPGA内部目的寄存器(终点)的数据路径,其目的是要通过提供要求的方式来使得综合工具vivado满足所有FPGA内部寄存器的建立时间要求和保持时间要求。

(2)管脚到寄存器

路径1,上游器件通过FPGA管脚到FPGA的寄存器的时序路径,即pin2reg(管脚到寄存器),需要对其进行约束以满足FPGA端寄存器的建立时间和保持时间要求。

路径1约束的是上游器件的源寄存器(起点)和FPGA内部的目的寄存器(终点)的数据路径,其目的是要满足后端即FPGA内部寄存器的建立时间要求和保持时间要求。

路径1可以视为是路径2的一种,只不过路径1的源寄存器和目的寄存器都在FPGA内部,而路径2的源寄存器在上游器件中。

(3)寄存器到管脚

路径3,FPGA管脚到下游器件的寄存器的时序路径,即reg2pin(寄存器到管脚),需要对其进行约束以满足下游器件的寄存器的建立时间和保持时间要求。

路径3约束的是FPGA内部的源寄存器(起点)和下游器件的目的寄存器(终点)的数据路径,其目的是要满足前端即FPGA内部寄存器的建立时间要求和保持时间要求。

路径3同样可以视为是路径2的一种,只不过路径1的源寄存器和目的寄存器都在FPGA内部,而路径3的目的寄存器在下游器件中。

(4)管脚到管脚

路径4,FPGA管脚到FPGA管脚的时序路径(不通过任何寄存器),其本质上是纯组合逻辑电路,仅仅需要将其值约束在一个指定范围,不需要满足建立时间和保持时间要求。

路径4中不存在任何寄存器,通常都是纯组合逻辑或者走线延迟等,所以也就不需要满足寄存器的建立时间要求和保持时间要求。需要的仅仅是根据开发需求约束其延迟的最小值和最大值。

路径1、2、3实际上都是对寄存器到寄存器之间的数据路径之间的约束,而路径4则是约束纯组合逻辑。

由于寄存器的采样往往都发生在时钟的边沿,所以目的寄存器采样的值实际上是上个时钟周期的源寄存器的值,也就是说在源寄存器与目的寄存器之间其采样时间相差一个时钟周期。

- 发射沿(Launch Edge) :是源寄存器采样的时间点,也是时序分析路径的起点

- 锁存沿(Latch Edge):是目的寄存器采样的时间点,也是时序分析路径的终点

由于2个寄存器之间存在的组合逻辑和走线延迟等,使得在发射沿采样到的数据需要一定的时间才能到达后级的锁存沿,这个时间就被称为数据到达时间(Data Arrival Time)。

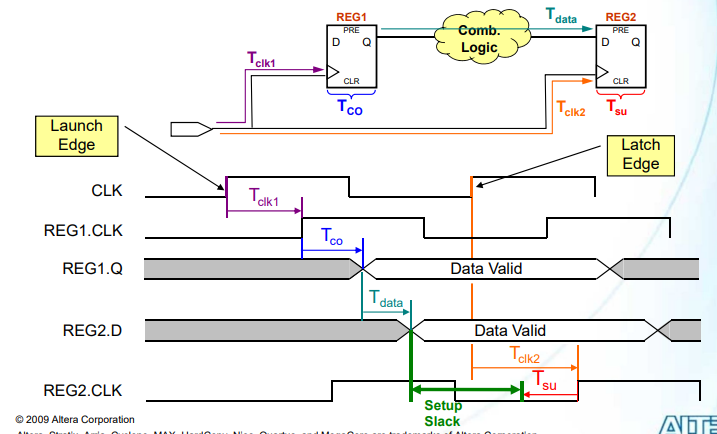

如上图,在计算数据到达时间时,存在3个时间参数:

- Tclk1:时钟信号从起点到达源寄存器REG1的时钟端口的时钟网络延时,产生原因一般是走线延迟

- Tco:源寄存器REG1内部的数据输出延迟,这个延迟时间是寄存器的固有属性,只和使用的FPGA芯片型号有关

- Tdata:数据从源寄存器REG1输出Q端到下级目的寄存器REG2的数据输入D之间的延时,一般是组合逻辑器件产生的固有延时和走线延时

根据上图可以算出数据到达时间:Data Arrival Time = launch edge + Tclk1 + Tco +Tdata

时序约束的本质就是要满足所有寄存器的建立时间要求和保持时间要求,所以在数据经过一定的延迟从源寄存器到达目的寄存器后,同样需要满足目的寄存器的建立时间要求(Tsu)。

如上图,在计算数据需求时间--建立时间时,存在2个时间参数:

- Tclk2:时钟信号从起点到达目的寄存器REG2的时钟端口的时钟网络延时,产生原因一般是走线延迟

- Tsu :在时钟有效边沿到达之间,输入数据必须保持不变的时间,这意味着上级寄存器的输入至少要在这之前就保持稳定

根据上图可以算出: Data Required Time + Tsu = latch edge + Tclk2 ,即 Data Required Time = latch edge + Tclk2 - Tsu

数据需求时间--建立时间,实际上是一种对石中盐到来之前数据保持稳定的最极端时间要求。比如为了满足目的寄存器的建立时间要求,计算得到上级寄存器的输出必须至少在3ns之前即保持稳定,这也就意味着上级数据能到达的最晚时间是3ns,那么1ns、2ns到达自然是可以的。

建立时间和保持时间是寄存器的2个固定需求属性,所以在数据经过一定的延迟从源寄存器到达目的寄存器后,同样需要满足目的寄存器的保持时间要求(Th)。

如上图,在计算数据需求时间--保持时间时,存在2个时间参数:

- Tclk2:时钟信号从起点到达目的寄存器REG2的时钟端口的时钟网络延时,产生原因一般是走线延迟

- Th:在时钟有效边沿到达之后,输入数据必须保持不变的时间,这意味着上级寄存器的输入至少要在这之后才能发生变化

所以可以算出: Data Required Time = latch edge + Tclk2 + Th

数据需求时间--建立时间实际上是一种对数据到来之前保持稳定的最极端的时间要求,比如为了满足目的寄存器的建立时间要求,计算得到上级寄存器的输出必须至少在时间刻度3ns之前即保持不变,这也就意味着上级数据能到达的最晚时间是3ns,那么1ns、2ns到达自然是可以的。

如果数据在1ns即到达了目的寄存器,那么建立时间裕量就是3ns-1ns = 2ns,那么这个裕量有什么作用呢或者说代表着什么?前面我们知道到寄存器之间可能会存在一段组合逻辑和走线延迟,如果你的设计中某2个寄存器之间的建立时间裕量是2ns,则意味着你还有空间去折腾,比如寄存器彼此之间还可以增加一些组合逻辑器件或者更长的走线。

根据上图,可以算出: Setup Slack = Data Required Time – Data Arrival Time,即Setup Slack = (latch edge + Tclk2 - Tsu ) – (launch edge + Tclk1 + Tco +Tdata )= (latch edge - launch edge) +(Tclk2 - Tclk1 )- (Tsu + Tco +Tdata)= Tperiod + Tskew - (Tsu + Tco +Tdata)。

如果Setup Slack为正,则说明数据在规定的时间内达到了目的寄存器;反之,则认为数据并没有在规定的时间达到目标,此时REG2锁存的数据很有可能是亚稳态状态。

数据需求时间--保持时间实际上是一种对时钟沿到来之后数据保持稳定的最极端的时间要求,比如为了满足目的寄存器的保持时间要求,计算得到上级寄存器的输出必须至少在时间刻度3ns之前都保持不变,这也就意味着上级数据能变化的最早时间是3ns,那么4ns、5ns到达自然是可以的。

如果数据在5ns处才在目的寄存器发生了变化,那么保持时间裕量就是5ns-3ns = 2ns。

根据上图,可以算出:Hold Slack = Data Arrival Time - Data Required Time,即Hold Slack = (latch edge + Tclk1 + Tco +Tdata) - (latch edge + Tclk2 + Th)= (Tco +Tdata - Th)-(Tclk2 - Tclk1)+ (latch edge - latch edge)= (Tco +Tdata - Th) - Tskew 。

如果Hold Slack为正,则认为数据在被锁存的时候有足够多的稳定时间,是有效的;反之则认为数据可能是亚稳态状态。

搞明白了这些概念,那么静态时序分析其实也就很简单了。上文出现了很多的公式,看起来有点晦涩难懂,但是没关系,这些公示实际上仅仅是起到一个辅助理解时序分析的作用,并不需要去记忆,更也不需要熟练掌握这些公式来生搬硬套时序分析。因为现在的综合工具已经足够智能了,你只需要提出时序约束的要求,综合工具vivado自然会对这些路径一一进行计算,你所要做的仅仅是找到时序裕量为负的路径并想办法改善即可。

此外,通过对上面公式的分析,可以让我们更好的了解静态时序分析的本质。

根据上文有(1)和(2)两式:

- 建立时间裕量:Setup Slack = Tperiod + Tskew - (Tsu + Tco +Tdata)----(1)

- 保持时间裕量:Hold Slack = (Tco +Tdata - Th) - Tskew ----(2)

其中,Tperiod 是时钟周期;Tskew 是寄存器之间的时钟偏差,产生的原因是时钟到达不同的寄存器的时钟端口有延迟;Tsu 与 Th分别是寄存器的建立时间要求和保持时间要求,这是寄存器的固有属性,只和FPGA的型号相关;Tco 是从寄存器的输入端口到输出端口所需要的延时时间,同样是寄存器的固有属性;Tdata是寄存器之间的组合逻辑和走线延迟等之和,这与具体设计有关,平时我们大多都是通过减少Tdata来使得时间裕量为正,以此实现设计的时序收敛。

Tskew实际上是一个可以被忽略掉的较小值,所以把它去掉,再对 (1)和(2)两式做变形(Slack>0需被满足),然后有(3)和(4)两式

- Tperiod >(Tsu + Tco +Tdata)----(3)

- (Tco +Tdata ) > Th ----(4)

(3)式子中的(Tsu + Tco +Tdata)代表数据从源寄存器到目的寄存器所消耗的时间,即(Tsu + Tco +Tdata)< Tperiod 表示数据从源寄存器的采样时刻传到目的寄存器的采样时刻,不能超过一个时钟周期。如果数据传输超过一个时钟周期,那么就会导致目的寄存器器开始采样的时候,从源寄存器出发的数据还没有传过来。

对于(4)式可以两边同时加上Tsu ,得到(5)式:

- (Tco +Tdata + Tsu ) > (Th + Tsu) ----(5)

(5)式子中的(Tsu + Tco +Tdata)代表数据从源寄存器到目的寄存器所消耗的时间,(Th + Tsu)是建立时间和保持时间之和,即寄存器的采样窗口时间。那么(Tsu + Tco +Tdata) > Th + Tsu表示数据从源寄存器的采样时刻传到目的寄存器的采样时刻,至少要大于寄存器的采样窗口。假如数据传输时间不大于采样窗口,则意味着数据的传输是特别快的,有可能目的寄存器开始采样时,源寄存器的采样仍没有结束,如果这个时候输入端数据有变化,那么不仅源寄存器处于亚稳态,目的寄存器也将处于亚稳态!

所以,数据传输延时既不能太大以至于超过一个时钟周期,也不能太小以至于小于触发器采样窗口的宽度。这就是静态时序分析的物理意义了。

导读:随着叮咚买菜业务的发展,不同的业务场景对数据分析提出了不同的需求,他们希望引入一款实时OLAP数据库,构建一个灵活的多维实时查询和分析的平台,统一数据的接入和查询方案,解决各业务线对数据高效实时查询和精细化运营的需求。经过调研选型,最终引入ApacheDoris作为最终的OLAP分析引擎,Doris作为核心的OLAP引擎支持复杂地分析操作、提供多维的数据视图,在叮咚买菜数十个业务场景中广泛应用。作者|叮咚买菜资深数据工程师韩青叮咚买菜创立于2017年5月,是一家专注美好食物的创业公司。叮咚买菜专注吃的事业,为满足更多人“想吃什么”而努力,通过美好食材的供应、美好滋味的开发以及美食品牌的孵

C#实现简易绘图工具一.引言实验目的:通过制作窗体应用程序(C#画图软件),熟悉基本的窗体设计过程以及控件设计,事件处理等,熟悉使用C#的winform窗体进行绘图的基本步骤,对于面向对象编程有更加深刻的体会.Tutorial任务设计一个具有基本功能的画图软件**·包括简单的新建文件,保存,重新绘图等功能**·实现一些基本图形的绘制,包括铅笔和基本形状等,学习橡皮工具的创建**·设计一个合理舒适的UI界面**注明:你可能需要先了解一些关于winform窗体应用程序绘图的基本知识,以及关于GDI+类和结构的知识二.实验环境Windows系统下的visualstudio2017C#窗体应用程序三.

1.postman介绍Postman一款非常流行的API调试工具。其实,开发人员用的更多。因为测试人员做接口测试会有更多选择,例如Jmeter、soapUI等。不过,对于开发过程中去调试接口,Postman确实足够的简单方便,而且功能强大。2.下载安装官网地址:https://www.postman.com/下载完成后双击安装吧,安装过程极其简单,无需任何操作3.使用教程这里以百度为例,工具使用简单,填写URL地址即可发送请求,在下方查看响应结果和响应状态码常用方法都有支持请求方法:getpostputdeleteGet、Post、Put与Delete的作用get:请求方法一般是用于数据查询,

Ⅰ软件测试基础一、软件测试基础理论1、软件测试的必要性所有的产品或者服务上线都需要测试2、测试的发展过程3、什么是软件测试找bug,发现缺陷4、测试的定义使用人工或自动的手段来运行或者测试某个系统的过程。目的在于检测它是否满足规定的需求。弄清预期结果和实际结果的差别。5、测试的目的以最小的人力、物力和时间找出软件中潜在的错误和缺陷6、测试的原则28原则:20%的主要功能要重点测(eg:支付宝的支付功能,其他功能都是次要的)80%的错误存在于20%的代码中7、测试标准8、测试的基本要求功能测试性能测试安全性测试兼容性测试易用性测试外观界面测试可靠性测试二、质量模型衡量一个优秀软件的维度①功能性功

需求:要创建虚拟机,就需要给他提供一个虚拟的磁盘,我们就在/opt目录下创建一个10G大小的raw格式的虚拟磁盘CentOS-7-x86_64.raw命令格式:qemu-imgcreate-f磁盘格式磁盘名称磁盘大小qemu-imgcreate-f磁盘格式-o?1.创建磁盘qemu-imgcreate-fraw/opt/CentOS-7-x86_64.raw10G执行效果#ls/opt/CentOS-7-x86_64.raw2.安装虚拟机使用virt-install命令,基于我们提供的系统镜像和虚拟磁盘来创建一个虚拟机,另外在创建虚拟机之前,提前打开vnc客户端,在创建虚拟机的时候,通过vnc

ES一、简介1、ElasticStackES技术栈:ElasticSearch:存数据+搜索;QL;Kibana:Web可视化平台,分析。LogStash:日志收集,Log4j:产生日志;log.info(xxx)。。。。使用场景:metrics:指标监控…2、基本概念Index(索引)动词:保存(插入)名词:类似MySQL数据库,给数据Type(类型)已废弃,以前类似MySQL的表现在用索引对数据分类Document(文档)真正要保存的一个JSON数据{name:"tcx"}二、入门实战{"name":"DESKTOP-1TSVGKG","cluster_name":"elasticsear

我正在寻找用于Rails的优质管理插件。似乎大多数现有的插件/gem(例如“restful_authentication”、“acts_as_authenticated”)都围绕着self注册等展开。但是,我正在寻找一种功能齐全的基于管理/管理角色的解决方案——但不是简单地附加到另一个非基于角色的解决方案。如果我找不到,我想我会自己动手......只是不想重新发明轮子。 最佳答案 RyanBates最近做了两个关于授权的railscast(注意身份验证和授权之间的区别;身份验证检查用户是否如她所说的那样,授权检查用户是否有权访问资源

我正在根据Rakefile中的现有测试文件动态生成测试任务。假设您有各种以模式命名的单元测试文件test_.rb.所以我正在做的是创建一个以“测试”命名空间内的文件名命名的任务。使用下面的代码,我可以用raketest:调用所有测试require'rake/testtask'task:default=>'test:all'namespace:testdodesc"Runalltests"Rake::TestTask.new(:all)do|t|t.test_files=FileList['test_*.rb']endFileList['test_*.rb'].eachdo|task|n

我想要像“嘿那里”这样的东西变成,例如,#316583。我希望将任意长度的字符串“归结”为十六进制颜色。我不知道从哪里开始。我在想,每个字符串的MD5散列都是不同的-但如何将该散列转换为十六进制颜色数字? 最佳答案 你可以只取几位前几位:require'digest/md5'color=Digest::MD5.hexdigest('Mytext')[0..5] 关于ruby-如何使用Ruby基于字母数字字符串生成颜色?,我们在StackOverflow上找到一个类似的问题:

(本文是网络的宏观的概念铺垫)目录计算机网络背景网络发展认识"协议"网络协议初识协议分层OSI七层模型TCP/IP五层(或四层)模型报头以太网碰撞路由器IP地址和MAC地址IP地址与MAC地址总结IP地址MAC地址计算机网络背景网络发展 是最开始先有的计算机,计算机后来因为多项技术的水平升高,逐渐的计算机变的小型化、高效化。后来因为计算机其本身的计算能力比较的快速:独立模式:计算机之间相互独立。 如:有三个人,每个人做的不同的事物,但是是需要协作的完成。 而这三个人所做的事是需要进行协作的,然而刚开始因为每一台计算机之间都是互相独立的。所以前面的人处理完了就需要将数据