因为没有找到相关例程,板子也是不是官方的。因此在综合编译时遇到一些警告和错误,在这里记录一下,写的不是很正确,也希望有大佬能够指点一二。

[Constraints 18-5210] No constraints selected for write.

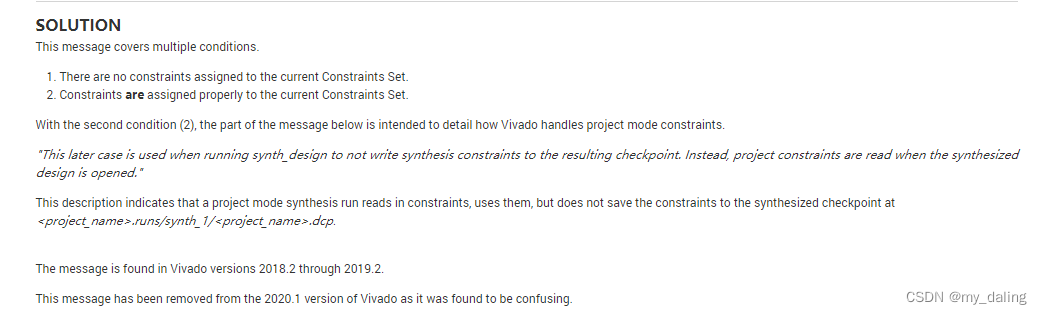

Resolution: This message can indicate that there are no constraints for the design, or it can indicate that the used_in flags are set such that the constraints are ignored. This later case is used when running synth_design to not write synthesis constraints to the resulting checkpoint. Instead, project constraints are read when the synthesized design is opened.

[Constraints 18-5210] No constraints selected for write.

警告设计中无约束,实际上我是有约束文件的,在XILINX官方论坛上找到如下解释:

The message is found in Vivado versions 2018.2 through 2019.2.

This message has been removed from the 2020.1 version of Vivado as it was found to be confusing.

大概是由于版本bug,在2018.2和2019.2中可能会出现此警告,不会造成影响因此可以忽略该警告。

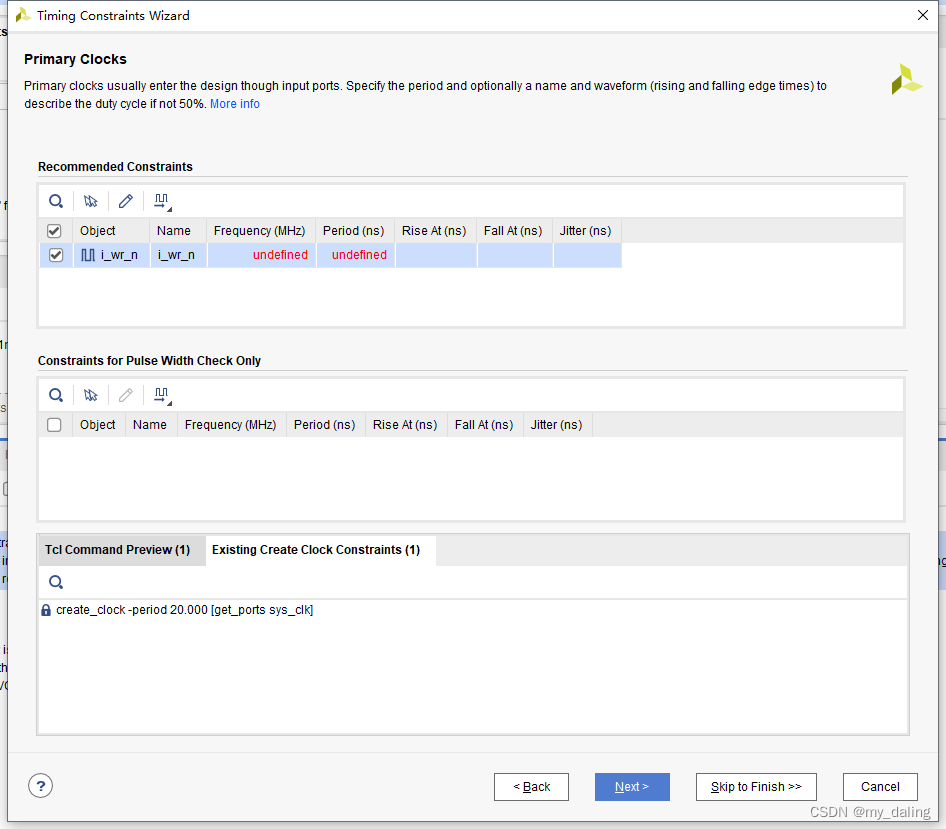

在Timing Constraints Wizard的截图中可以看到,本应该被约束的系统时钟sys_clk变成了一个普通IO输入,或者同时出现时钟和普通io需要被约束情况。

没有时钟或找不到时钟是因为截图下方可以看到,sys_clk其实已经被约束过了,因为我使用了PLL的IP核,系统时钟进来直接接PLL后输出,系统默认对其进行了约束。

普通io出现在里面是因为我在一个模块里将其作为上升沿触发了(不好的写法)。"always@(posedge i_wr_n or negedge rst_n)",这样写的话,编译器会把它当作时钟处理,自然就会出现在时钟约束里等你约束了,这里建议如果是需要上升沿处理可以进行边沿检测,将上升沿转化为一个clock的高电平。或者按照提示添加约束。

不然运行run implementation会报错。

在生成比特流时出现如下警告:

[DRC CFGBVS-1] Missing CFGBVS and CONFIG_VOLTAGE Design Properties: Neither the CFGBVS nor CONFIG_VOLTAGE voltage property is set in the current_design. Configuration bank voltage select (CFGBVS) must be set to VCCO or GND, and CONFIG_VOLTAGE must be set to the correct configuration voltage, in order to determine the I/O voltage support for the pins in bank 0. It is suggested to specify these either using the 'Edit Device Properties' function in the GUI or directly in the XDC file using the following syntax:

set_property CFGBVS value1 [current_design]

#where value1 is either VCCO or GND

set_property CONFIG_VOLTAGE value2 [current_design]

#where value2 is the voltage provided to configuration bank 0

Refer to the device configuration user guide for more information.

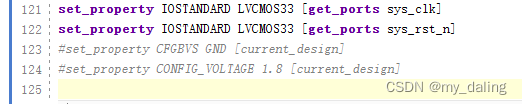

这是由于没有正确约束配置电平,如下演示:

根据提示对其约束

set_property CFGBVS value1 [current_design]

#where value1 is either VCCO or GND

set_property CONFIG_VOLTAGE value2 [current_design]

#where value2 is the voltage provided to configuration bank 0

这里需要注意约束电压要和原理图相对应。一般FPGA配置电压为1.8V,对应CFGBVS要约束为GND,如果CONFIG_VOLTAGE配置电压选择3.3,那么对应CFGBVS要约束为VCCO。

在FPGA管脚原理图连接时可以参考官方文档,就算都是用户io,也尽量不要随意配置,尤其是多功能复用io,在文档中有注明

我知道Ruby是动态和强类型的,但据我所知,由于每个参数缺少显式类型表示法(或契约),当前语法不允许在编译时检查参数类型。如果我想执行编译时类型检查,我有哪些(实际成熟的)选项?更新我的意思是类型检查类似于典型的静态类型语言。比如C。例如,C函数表示每个参数的类型,编译器检查传入的参数是否正确。voidfunc1(structAAAaaa){structBBBbbb;func1(bbb);//Wrongtype.Compiletimeerror.}作为另一个例子,Objective-C通过放置显式类型信息来做到这一点。-(id)method1:(AAA*)aaa{BBB*bbb=[[A

FPGA时钟和时钟域时钟树所谓时钟树为FPGA内部资源,分:全局时钟树,区域时钟树,IO时钟树原则上优先使用全局时钟树,在GT接口上使用IO时钟树,一般工具也会对GT时钟加以限制;时钟树使用方式正确的物理连接FPGA会由物理管脚专门用于全局时钟设置,通过查询数据手册可以在PCB设计阶段进行确认,当外部时钟接入此管脚时,工具会自动占有全局时钟树资源,当接入普通信号时不会分配时钟树资源;恰当的代码描述原语的使用,即BUFG的使用,可以将PLL的输出等内部时钟进行全局时钟资源的分配;IO时钟资源需要参考相应接口手册,以ultrascale的GTH为例,其JESD204的时钟方案针对不同的子类会由不同

外部SPIFLASH:MicronN25Q128A13ESE40G(128Mbit(16MByte))FPGA:XC7A100T CPU:Microblaze第一种情况:Microblaze在简单的应用,比如运行LED,IIC,SPI,UART之类的低俗接口驱动,或做一些简单的辅助型工作时,一般生成的applicationelf文件都不大,在10几KB或者几十,百几KB,此时使用FPGA内部的BRAM资源已经足够。XC7A100T本身就有600几KB的BRAM资源。这种情况下直接将硬件流文件和elf文件合并为download.bit文件,在直接烧录到外部SPIFLAH即可。1.Xilinx--

1FPGA启动流程图1 7SerialsFPGA配置流程1.1DevicePower-Up1.2ClearConfigurationMemory在上电后的任何时间内,可以对Slave-FPGA配置存储器(BlockRAM)进行复位处理。复位方式是将PROGRAM_B信号拉低(下降沿有效)。1.3SampleModePins当复位完成后,INIT_B恢复高电平,Slave-FPGA对M[2:0]模式引脚进行采样,然后开始在CCLK上升沿接收配置数据。1.4Synchronization在接收配置数据前,Slave-FPGA首先进行总线位宽检测。主机发送的配置文件中,“BusWidthAutoDe

文章目录1、行为级与RTL级的区别1.1RTL级(可综合成门级电路)1.2行为级2、关于LUT2.1LUT是什么2.2N维查找表2.3FPGA中的LUT3、`include和条件编译4、写异步D触发器(扬智电子笔试)4.1八位同步D触发器4.2具有异步清零,同步复位信号功能的D触发器5、静态、动态时序分析的优缺点(威盛VIA2003.11.06上海笔试试题)6、采用二选一多路器mux2和inv非门实现异或操作(飞利浦-大唐笔试)7、寄存器和锁存器的区别,为什么多用寄存器,行为级描述中锁存器如何产生8、D触发器实现2分频的Verilog描述(汉王笔试)9、D触发器实现带同步高置数和异步高复位端的

我正在尝试为我的项目设置webpack。该项目足够大,并提供多种语言。我希望我的每个入口点都以每种语言作为单独的文件提供。我的语言文件不仅仅是普通的JSON,而是JavaScript。所以i18n插件不符合我的需求。解决办法好像是i18nplugin:varlanguages=['en','fr','de'];module.exports=languages.map(function(lang){return{name:lang,//someotherlanguage-dependentconfig}})然后在我的一些脚本中,我想使用环境变量要求本地化文件:varlang=...;//

如何使用FPGA加速机器学习算法如何使用FPGA加速机器学习算法 当前,AI因为其CNN(卷积神经网络)算法出色的表现在图像识别领域占有举足轻重的地位。基本的CNN算法需要大量的计算和数据重用,非常适合使用FPGA来实现。上个月,RalphWittig(XilinxCTOOffice的卓越工程师)在2016年OpenPower峰会上发表了约20分钟时长的演讲并讨论了包括清华大学在内的中国各大学研究CNN的一些成果。在这项研究中出现了一些和CNN算法实现能耗相关的几个有趣的结论:①限定使用片上Memory;②使用更小的乘法器;③进行定点匹配:相对于32位定点或浮点计算,将定点计算结果精度降为16

我遇到的问题是,一旦我importvue,vue的包装元素(在我的例子中是#app)将被替换为以下注释控制台中没有错误,webpack编译正常,但是我确实从vue的mounted方法获取了控制台日志。我的index.htmlDocumentsomecontent{{test}}webpack.config.jsconstpath=require('path');module.exports={entry:'./src/app.js',output:{filename:'bundle.js',path:path.resolve(__dirname,'dist')}}源/app.jsimp

1)实验平台:正点原子MPSoC开发板2)平台购买地址:https://detail.tmall.com/item.htm?id=6924508746703)全套实验源码+手册+视频下载地址:http://www.openedv.com/thread-340252-1-1.html第二十三章DDS信号发生器实验DDS(DirectDigitalSynthesizer)即直接数字式频率合成器,是一种新型的频率合成技术。与传统的频率合成器相比,DDS具有相对带宽大,频率转换时间短,稳定性好,分辨率高,可灵活产生多种信号等优点。较容易实现频率、相位及幅度的数控调制,因此,在现代电子系统及设备的频率源

我正在寻找一种在编译时在Javascript全局命名空间中定义Clojurescript函数的方法。我所说的编译时是指我希望Clojurescript编译器输出:functionsome_fn(){}。我知道这不是惯用的,一切都应该驻留在命名空间中,但我所处的环境迫使我这样做。因此,理想情况下,类似于(defn^:globalsome-fn[])的工作方式类似于:export的工作方式,但忽略了namespace。我知道使用goog.global定义全局函数的运行时方法,例如(set!goog.global.someFunctionsome-clojure-fn)但这在我的环境中不起作