SPI接口驱动模块设计

写在前面:

FPGA实现SPI协议读写FLASH系列相关文章:

SPI通信协议

【FPGA】FPGA实现SPI协议读写FLASH(一)----- M25P16操作概述

在上篇文章中对FLASH(M25P16)读写操作及指令等做了详细介绍,本文将通过SPI协议原理,设计SPI通信接口,实现FPGA与FLASH进行通信。

本项目中所使用的开发板型号:Cyclone IV E (EP4CE6F17C8),FLASH型号:M25P16。

SPI接口驱动模块(spi_interface)主要根据SPI协议原理架起FPGA与FLASH数据传输的“桥梁”,将从SPI读写控制模块接收到的指令、地址、数据字节严格按照SPI协议传输给FLASH,并接收从FLASH读回的数据,发送给SPI读写控制模块。

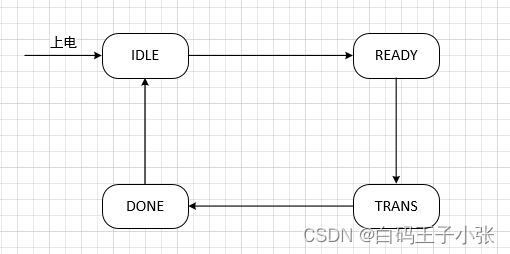

状态转移图如下:

状态说明:

IDLE:空闲状态,等待读写控制模块发起数据传输请求。

READY:准备传输数据。

TRANS:数据传输状态,根据SPI协议发送或接收数据。

DONE:数据传输结束。

| Port | I/O Type | Description |

|---|---|---|

| clk | input | 时钟信号 |

| rst_n | input | 复位信号 |

| req | input | 读/写数据请求 |

| din[7:0] | input | 要传输给FLASH的数据 |

| rdout[7:0] | output | 从FLASH读回的数据 |

| rw_done | output | 读/写一字节数据完成标志 |

| sclk | output | 同步时钟 |

| cs_n | output | 片选信号 |

| mosi | output | 主机输出,从机输入信号 |

| miso | input | 主机输入,从机输出信号 |

// **************************************************************

// Author: Zhang JunYi

// Create Date: 2022.11.15

// Design Name: spi_flash

// Module Name: spi_interface

// Target Device: Cyclone IV E (EP4CE6F17C8), FLASH(M25P16)

// Tool versions: Quartus Prime 18.1

// Description: SPI读写FLASH工程SPI接口模块

// **************************************************************

`include "param.v"

module spi_interface (

input clk ,

input rst_n ,

// flash_control

input req , // 读/写数据请求

input [7:0] din , // 要写入的数据

output [7:0] rdout , // 读回的数据

output rw_done , // 读写一字节数据完成标志

// M25P16

output sclk ,

output cs_n ,

output mosi ,

input miso

);

// 参数定义

localparam IDLE = 4'b0001 ,

READY = 4'b0010 ,

TRANS = 4'b0100 ,

DONE = 4'b1000 ;

// 信号定义

reg [3:0] state_c ;

reg [3:0] state_n ;

reg [4:0] cnt_sclk ; // sclk计数器

wire add_cnt_sclk ;

wire end_cnt_sclk ;

reg [4:0] cnt_bit ; // sclk计数器

wire add_cnt_bit ;

wire end_cnt_bit ;

reg sclk_reg ; // 输出sclk寄存

reg tx_data ; // 数据输出寄存

reg [7:0] rx_data ; // 读回数据寄存

// 状态转移条件

wire idle2ready ;

wire ready2trans ;

wire trans2done ;

wire done2idle ;

// 状态机

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

state_c <= IDLE ;

end

else begin

state_c <= state_n ;

end

end

always @(*)begin

case (state_c)

IDLE: begin

if(idle2ready)

state_n = READY ;

else

state_n = state_c ;

end

READY: begin

if(ready2trans)

state_n = TRANS ;

else

state_n = state_c ;

end

TRANS: begin

if(trans2done)

state_n = DONE ;

else

state_n = state_c ;

end

DONE: begin

if(done2idle)

state_n = IDLE ;

else

state_n = state_c ;

end

default: state_n = IDLE ;

endcase

end

// 状态转移条件

assign idle2ready = state_c == IDLE && req ;

assign ready2trans = state_c == READY && (1'b1) ;

assign trans2done = state_c == TRANS && end_cnt_bit ;

assign done2idle = state_c == DONE && (1'b1) ;

// cnt_sclk

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_sclk <= 0 ;

end

else if(add_cnt_sclk)begin

if(end_cnt_sclk)begin

cnt_sclk <= 0 ;

end

else begin

cnt_sclk <= cnt_sclk + 1 ;

end

end

end

assign add_cnt_sclk = state_c == TRANS ;

assign end_cnt_sclk = add_cnt_sclk && (cnt_sclk == `SCLK_CYCLE - 1) ;

// sclk_reg

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

sclk_reg <= 1'b1 ;

end

else if(add_cnt_sclk && cnt_sclk == `SCLK_FALL)begin

sclk_reg <= 1'b0 ;

end

else if(add_cnt_sclk && cnt_sclk == `SCLK_RISE)begin

sclk_reg <= 1'b1 ;

end

end

// cnt_bit

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0 ;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0 ;

end

else begin

cnt_bit <= cnt_bit + 1 ;

end

end

end

assign add_cnt_bit = end_cnt_sclk ;

assign end_cnt_bit = add_cnt_bit && (cnt_bit == 7) ;

// tx_data

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

tx_data <= 1'b1 ;

end

else if(state_c == TRANS && cnt_sclk == `TRANS_S)begin

tx_data <= din[7 - cnt_bit] ;

end

else if(trans2done)begin

tx_data <= 1'b1 ;

end

end

// rx_data

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data <= 0 ;

end

else if(state_c == TRANS && cnt_sclk == `SAMP_S)begin

rx_data[7 - cnt_bit] <= miso ;

end

end

// 输出

assign rdout = rx_data ;

assign rw_done = trans2done ;

assign sclk = sclk_reg ;

assign cs_n = ~req ;

assign mosi = tx_data ;

endmodule

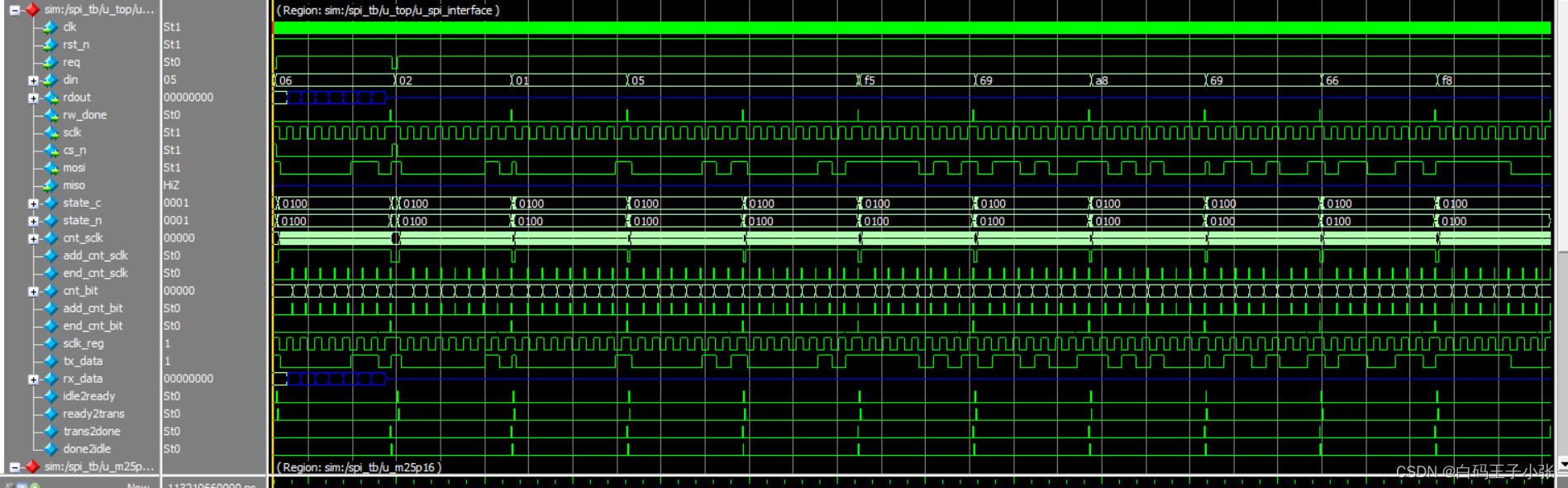

SPI接口模块发送数据:

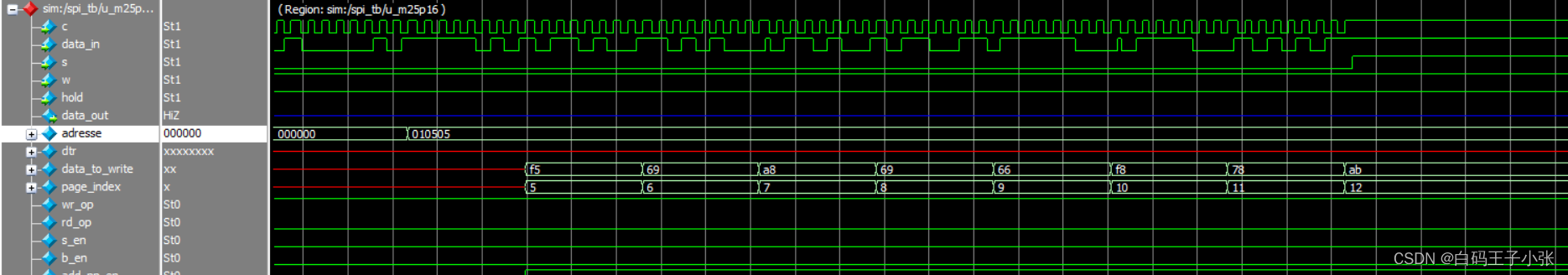

M25P16从机模型接收数据:

通过仿真分析,M25P16从机模型接收数据正确,SPI接口模块功能已实现。

假设我做了一个模块如下:m=Module.newdoclassCendend三个问题:除了对m的引用之外,还有什么方法可以访问C和m中的其他内容?我可以在创建匿名模块后为其命名吗(就像我输入“module...”一样)?如何在使用完匿名模块后将其删除,使其定义的常量不再存在? 最佳答案 三个答案:是的,使用ObjectSpace.此代码使c引用你的类(class)C不引用m:c=nilObjectSpace.each_object{|obj|c=objif(Class===objandobj.name=~/::C$/)}当然这取决于

作为我的Rails应用程序的一部分,我编写了一个小导入程序,它从我们的LDAP系统中吸取数据并将其塞入一个用户表中。不幸的是,与LDAP相关的代码在遍历我们的32K用户时泄漏了大量内存,我一直无法弄清楚如何解决这个问题。这个问题似乎在某种程度上与LDAP库有关,因为当我删除对LDAP内容的调用时,内存使用情况会很好地稳定下来。此外,不断增加的对象是Net::BER::BerIdentifiedString和Net::BER::BerIdentifiedArray,它们都是LDAP库的一部分。当我运行导入时,内存使用量最终达到超过1GB的峰值。如果问题存在,我需要找到一些方法来更正我的代

我有一个模型:classItem项目有一个属性“商店”基于存储的值,我希望Item对象对特定方法具有不同的行为。Rails中是否有针对此的通用设计模式?如果方法中没有大的if-else语句,这是如何干净利落地完成的? 最佳答案 通常通过Single-TableInheritance. 关于ruby-on-rails-Rails-子类化模型的设计模式是什么?,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.co

我有一个包含模块的模型。我想在模块中覆盖模型的访问器方法。例如:classBlah这显然行不通。有什么想法可以实现吗? 最佳答案 您的代码看起来是正确的。我们正在毫无困难地使用这个确切的模式。如果我没记错的话,Rails使用#method_missing作为属性setter,因此您的模块将优先,阻止ActiveRecord的setter。如果您正在使用ActiveSupport::Concern(参见thisblogpost),那么您的实例方法需要进入一个特殊的模块:classBlah

我将应用程序升级到Rails4,一切正常。我可以登录并转到我的编辑页面。也更新了观点。使用标准View时,用户会更新。但是当我添加例如字段:name时,它不会在表单中更新。使用devise3.1.1和gem'protected_attributes'我需要在设备或数据库上运行某种更新命令吗?我也搜索过这个地方,找到了许多不同的解决方案,但没有一个会更新我的用户字段。我没有添加任何自定义字段。 最佳答案 如果您想允许额外的参数,您可以在ApplicationController中使用beforefilter,因为Rails4将参数

我有一个用户工厂。我希望默认情况下确认用户。但是鉴于unconfirmed特征,我不希望它们被确认。虽然我有一个基于实现细节而不是抽象的工作实现,但我想知道如何正确地做到这一点。factory:userdoafter(:create)do|user,evaluator|#unwantedimplementationdetailshereunlessFactoryGirl.factories[:user].defined_traits.map(&:name).include?(:unconfirmed)user.confirm!endendtrait:unconfirmeddoenden

我刚刚被困在这个问题上一段时间了。以这个基地为例:moduleTopclassTestendmoduleFooendend稍后,我可以通过这样做在Foo中定义扩展Test的类:moduleTopmoduleFooclassSomeTest但是,如果我尝试通过使用::指定模块来最小化缩进:moduleTop::FooclassFailure这失败了:NameError:uninitializedconstantTop::Foo::Test这是一个错误,还是仅仅是Ruby解析变量名的方式的逻辑结果? 最佳答案 Isthisabug,or

我想获取模块中定义的所有常量的值:moduleLettersA='apple'.freezeB='boy'.freezeendconstants给了我常量的名字:Letters.constants(false)#=>[:A,:B]如何获取它们的值的数组,即["apple","boy"]? 最佳答案 为了做到这一点,请使用mapLetters.constants(false).map&Letters.method(:const_get)这将返回["a","b"]第二种方式:Letters.constants(false).map{|c

我的假设是moduleAmoduleBendend和moduleA::Bend是一样的。我能够从thisblog找到解决方案,thisSOthread和andthisSOthread.为什么以及什么时候应该更喜欢紧凑语法A::B而不是另一个,因为它显然有一个缺点?我有一种直觉,它可能与性能有关,因为在更多命名空间中查找常量需要更多计算。但是我无法通过对普通类进行基准测试来验证这一点。 最佳答案 这两种写作方法经常被混淆。首先要说的是,据我所知,没有可衡量的性能差异。(在下面的书面示例中不断查找)最明显的区别,可能也是最著名的,是你的

我一直致力于让我们的Rails2.3.8应用程序在JRuby下正确运行。一切正常,直到我启用config.threadsafe!以实现JRuby提供的并发性。这导致lib/中的模块和类不再自动加载。使用config.threadsafe!启用:$rubyscript/runner-eproduction'pSim::Sim200Provisioner'/Users/amchale/.rvm/gems/jruby-1.5.1@web-services/gems/activesupport-2.3.8/lib/active_support/dependencies.rb:105:in`co