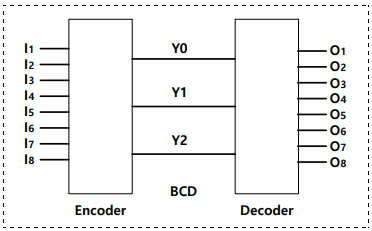

写在前面:本章将理解编码器与解码器、多路复用器与多路分解器的概念,通过使用 Verilog 实现多样的解码器与多路分解器,通过 FPGA 并使用 Verilog 实现。

解码器 (Decoder):执行转换和处理过程以将 Encoding 数据恢复到之前的电路。

编码器 (Encoder):将特定数据转换和处理为其他形式或格式的电路,以确保安全或缩小数据的大小。

编码器和解码器用于将任意两种符号体系相互转换。

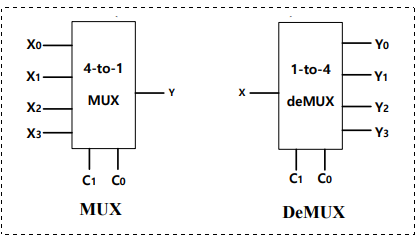

多路复用器 MUX (Multiplexer),能接收多个输入信号,按每个输入信号可恢复方式合成单个输出信号。复用器是一种综合系统,通常包含一定数目的数据输入,有一个单独的输出。

多路分解器 DeMUX (DeMultiplexer),是从一个输入接收资料,根据多条输出线中的输入,连接到预先选定的一条输出线的电路。

通常与带有 enable line 的解码器相同。

由于各自的功能特性,MUX 也被称为 Data Selctor(数据选择器),DeMUX 也被称为 Data Distributor(数据分配器)。

使用 AND 对电路进行 Verilog 编码,使用 NAND 结构对电路进行 Verilog 编码,通过 Verilog 的模拟结果完成真值表(2种),并比较两种形式的解码器。

💬 Design source:

`timescale 1ns / 1ps

module two_to_four_decoder(

input A, B,

output D1, D2, D3, D4

);

assign D1 = ~A&~B;

assign D2 = ~A&B;

assign D3 = A&~B;

assign D4 = A&B;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module two_to_four_decode_tb;

reg AA, BB;

wire D1, D2, D3, D4;

two_to_four_decoder u_two_to_four_decoder(

.A(AA),

.B(BB),

.D1(D2),

.D2(D2),

.D3(D3),

.D4(D4)

);

initial AA = 1'b0;

initial BB = 1'b0;

always AA = #100 ~AA;

always BB = #200 ~BB;

initial begin

#1000

$finish;

end

endmodule

🚩 运行结果如下:

使用 OR 对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。

💬 Design source:

`timescale 1ns / 1ps

module four_to_two_encoder(

input a, b, c, d,

output e0, e1

);

assign e0 = a|b;

assign e1 = a|c;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module four_to_two_encoder_tb;

reg aa, bb, cc, dd;

wire e0, e1;

four_to_two_encoder u_four_to_two_encoder(

.a(aa),

.b(bb),

.c(cc),

.d(dd),

.e0(e0),

.e1(e1)

);

initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

always aa = #100 ~aa;

always bb = #200 ~bb;

always cc = #400 ~cc;

always dd = #800 ~dd;

initial begin

#1000

$finish;

end

endmodule

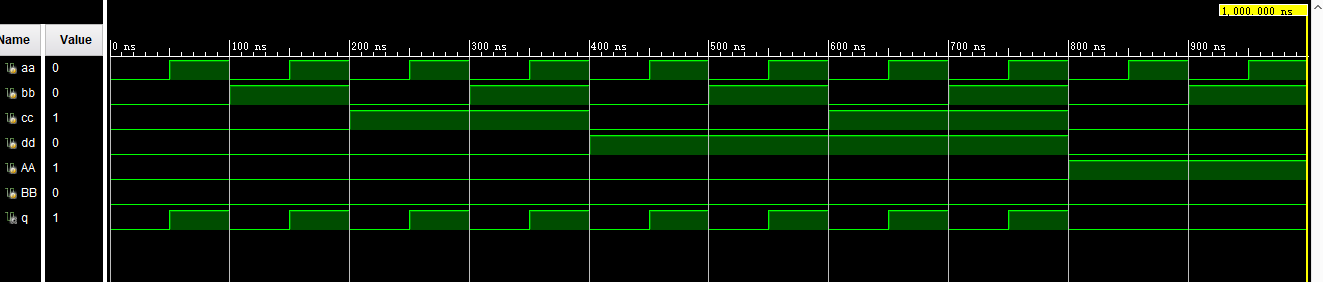

🚩 运行结果如下:

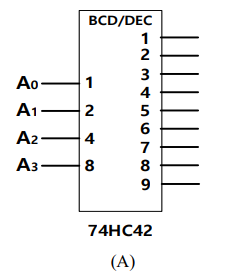

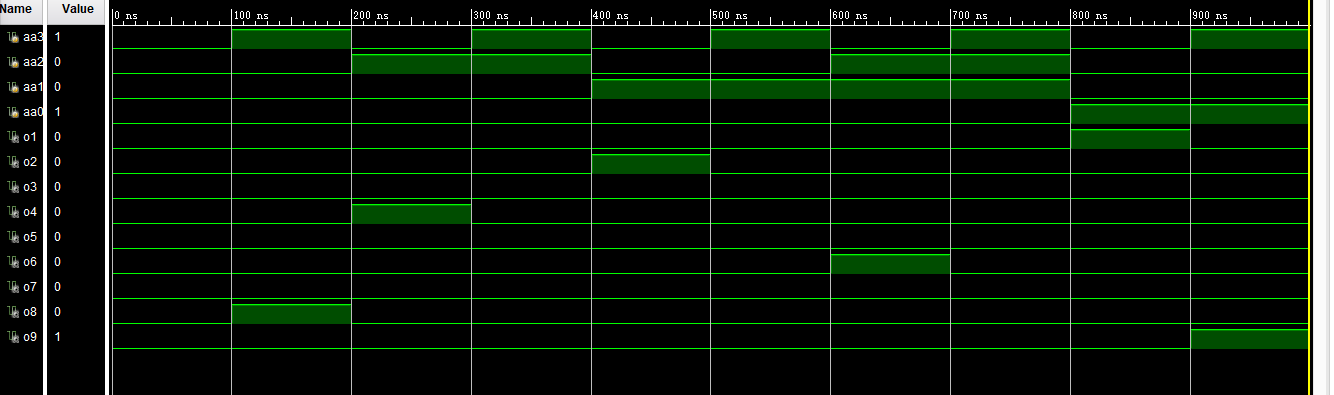

通过 Verilog 编码实现(A)的结构,通过 Verilog 的仿真结果完成真值表,并确认是否与理论中的Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module bcd_decoder(

input a3, a2, a1, a0,

output o1, o2, o3, o4, o5, o6, o7, o8, o9

);

assign o1 = ~a3&~a2&~a1&a0;

assign o2 = ~a3&~a2&a1&~a0;

assign o3 = ~a3&~a2&a1&a0;

assign o4 = ~a3&a2&~a1&~a0;

assign o5 = ~a3&a2&~a1&a0;

assign o6 = ~a3&a2&a1&~a0;

assign o7 = ~a3&a2&a1&a0;

assign o8 = a3&~a2&~a1&~a0;

assign o9 = a3&~a2&~a1&a0;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module bcd_decoder_tb;

reg aa3, aa2, aa1, aa0;

wire o1, o2, o3, o4, o5, o6, o7, o8, o9;

bcd_decoder u_bcd_decoder(

.a3(aa3),

.a2(aa2),

.a1(aa1),

.a0(aa0),

.o1(o1),

.o2(o2),

.o3(o3),

.o4(o4),

.o5(o5),

.o6(o6),

.o7(o7),

.o8(o8),

.o9(o9)

);

initial aa3 = 1'b0;

initial aa2 = 1'b0;

initial aa1 = 1'b0;

initial aa0 = 1'b0;

always aa3 = #100 ~aa3;

always aa2 = #200 ~aa2;

always aa1 = #400 ~aa1;

always aa0 = #800 ~aa0;

initial begin

#1000

$finish;

end

endmodule

🚩 运行结果如下:

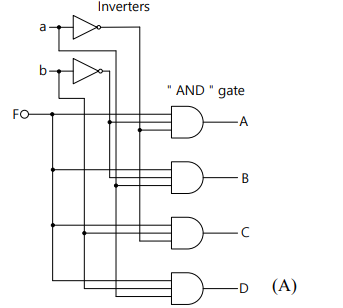

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。并确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module four_to_one_mux(

input a, b, c, d, A, B,

output q

);

assign q = (a&~B&~A)|(b&B&~A)|(c&~B&A)|(d&B&A);

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module four_to_one_mux_tb;

reg aa, bb, cc, dd, AA, BB;

wire q;

four_to_one_mux u_four_to_one_mux(

.a(aa),

.b(bb),

.c(cc),

.d(dd),

.A(AA),

.B(BB),

.q(q)

);

initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

initial AA = 1'b0;

initial BB = 1'b0;

always aa = #50 ~aa;

always bb = #100 ~bb;

always cc = #200 ~cc;

always dd = #400 ~dd;

always AA = #800 ~AA;

always BB = #1600 ~BB;

initial begin

#2000

$finish;

end

endmodule

🚩 运行结果如下:

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表,确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module one_to_four_mux(

input A, B, f,

output a, b, c, d

);

assign a = f&(~A&~B);

assign b = f&(~A&B);

assign c = f&(A&~B);

assign d = f&(A&B);

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module one_to_four_mux_tb;

reg AA, BB, ff;

wire a, b, c, d;

one_to_four_mux u_one_to_four_mux(

.A(AA),

.B(BB),

.f(ff),

.a(a),

.b(b),

.c(c),

.d(d)

);

initial AA = 1'b0;

initial BB = 1'b0;

initial ff = 1'b0;

always AA = #100 ~AA;

always BB = #200 ~BB;

always ff = #400 ~ff;

initial begin

#1000

$finish;

end

endmodule

🚩 运行结果如下:

📌 [ 笔者 ] Foxny,Akam

📃 [ 更新 ] 2023.3.5

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

给定一个数组a,什么是实现其组合直到第n的最佳方法?例如:a=%i[abc]n=2#Expected=>[[],[:a],[:b],[:c],[:a,b],[:b,:c],[:c,:a]] 最佳答案 做如下:a=%w[abc]n=30.upto(n).flat_map{|i|a.combination(i).to_a}#=>[[],["a"],["b"],["c"],["a","b"],#["a","c"],["b","c"],["a","b","c"]] 关于ruby-最多n的组合,我

我想合并多个事件记录关系例如,apple_companies=Company.where("namelike?","%apple%")banana_companies=Company.where("namelike?","%banana%")我想结合这两个关系。不是合并,合并是apple_companies.merge(banana_companies)=>Company.where("namelike?andnamelike?","%apple%","%banana%")我要Company.where("名字像?还是名字像?","%apple%","%banana%")之后,我会写代

我有一个熟悉的问题,看起来像是数学世界的排列/组合。如何通过ruby实现以下目标?badges="1-2-3"badge_cascade=[]badges.split("-").eachdo|b|badge_cascade["1","2","3"]ButIwantittobeis:=>["1","2","3","1-2","2-3","3-1","2-1","3-2","1-3","1-2-3","2-3-1","3-1-2"] 最佳答案 函数式方法:bs="1-2-3".split("-")strings=1.upto(bs.

在尝试解决“网格上的路径”问题时,我编写了代码defpaths(n,k)p=(1..n+k).to_ap.combination(n).to_a.sizeend代码工作正常,例如ifn==8andk==2代码返回45,这是正确的路径数。但是,当使用较大的数字时,代码非常慢,我正在努力想出如何加快这个过程。 最佳答案 与其构建组合数组只是为了计算它,不如编写function定义组合的数量。我敢肯定还有包含此功能和许多其他组合函数的gem。请注意,我使用的是gemDistribution对于Math.factorial方法,但这是另一种

对于一个电子商务应用程序,我试图将选项的散列(每个选项都有一系列选择)转换为代表这些选择组合的散列数组。例如:#Input:{:color=>["blue","grey"],:size=>["s","m","l"]}#Output:[{:color=>"blue",:size=>"s"},{:color=>"blue",:size=>"m"},{:color=>"blue",:size=>"m"},{:color=>"grey",:size=>"s"},{:color=>"grey",:size=>"m"},{:color=>"grey",:size=>"m"}]Input内部可能有额

目录一、inout在设计文件中的使用方法1.1、inout的第一种使用方法1.2、inout实现的第二种使用方法1.3、inout使用总结 二、inout在仿真测试中的使用方法一、inout在设计文件中的使用方法在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号)。比如,IIC总线中的SDA信号就是一个双向信号,QSPIFlash的四线操作的时候四根信号线均为双向信号。在Verilog中用关键字inout定义双向信号,这里总结一下双向信号的处理方法。1.1、inout的第一种使用方法 实际上,双向信号的本质是由一个三态门组成的,三态门可以输出高电平,低电

我大胆猜测将一个数组拼成另一个数组比将两个数组加在一起更快,但经过快速基准测试后我发现我错了。我假设解释器只会将splat转换为数组文字,而不必每次都对其调用+方法。那么,为什么+比splat更快?我使用了这个基准代码:deftest(trials=1000)head=[1,2,3]tail=100.times.to_at=Time.now.to_ftrials.timesdo|i|a=[head,*tail]endputs"splatdonein#{Time.now.to_f-t}"t=Time.now.to_ftrials.timesdo|i|a=head+tailendputs"

这里是初级程序员,只是想了解Ruby背后的过程sort使用飞船操作符时的方法.希望有人能帮忙。在以下内容中:array=[1,2,3]array.sort{|a,b|ab}...我明白sort一次比较一对数字,然后返回-1如果a属于b之前,0如果它们相等,或者1如果a应该遵循b.但是在降序排序的情况下,像这样:array.sort{|a,b|ba}...到底发生了什么?是否sort还是比较ab然后翻转结果?或者它是在解释return的-1,0和1具有相反的行为?换句话说,为什么要像这样将变量放在block中:array.sort{|b,a|ba}...结果与第一个示例中的排序模式相同?

link有两个组件:componenta_id和componentb_id。为此,在Link模型文件中我有:belongs_to:componenta,class_name:"Component"belongs_to:componentb,class_name:"Component"validates:componenta_id,presence:truevalidates:componentb_id,presence:truevalidates:componenta_id,uniqueness:{scope::componentb_id}validates:componentb_id