文章目录

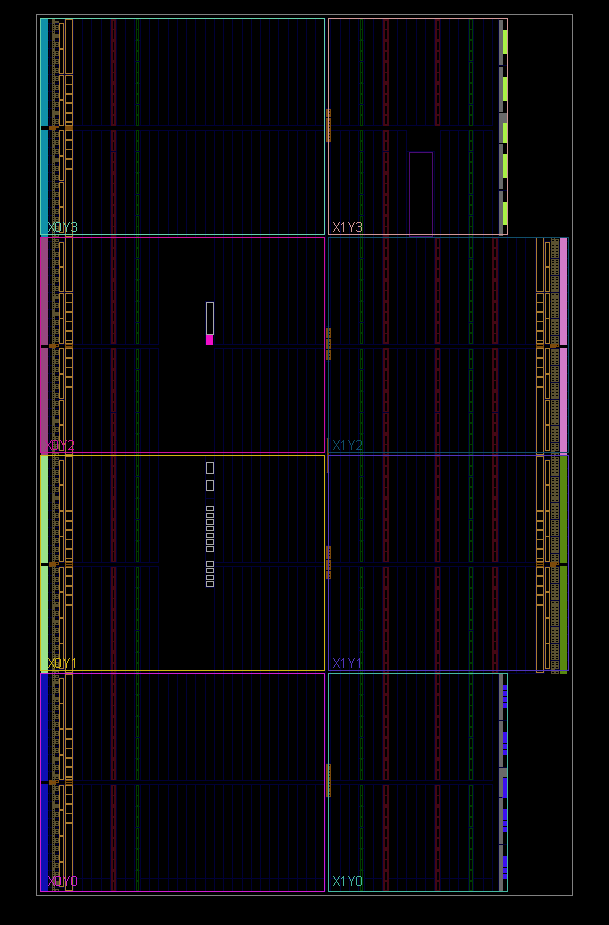

我们可以用vivado打开一个器件的device视图:

可以看到这些花里胡哨的五颜六色就分别代表了FPGA的底层硬件单元,主要有:可编程输入输出单元(IOB)、可编程逻辑单元(CLB)、时钟管理单元(MMCM/PLL)、BRAM、布线资源、内嵌的底层功能单元和内嵌专用硬件模块。其中最为主要的是可编程输出输出单元(IOB)、可编程逻辑单元(CLB)和布线资源。

而我们今天的主角可编程逻辑单元CLB则在上图中蓝色的若隐若现的位置,我们需要把它放大才能更好地观察:

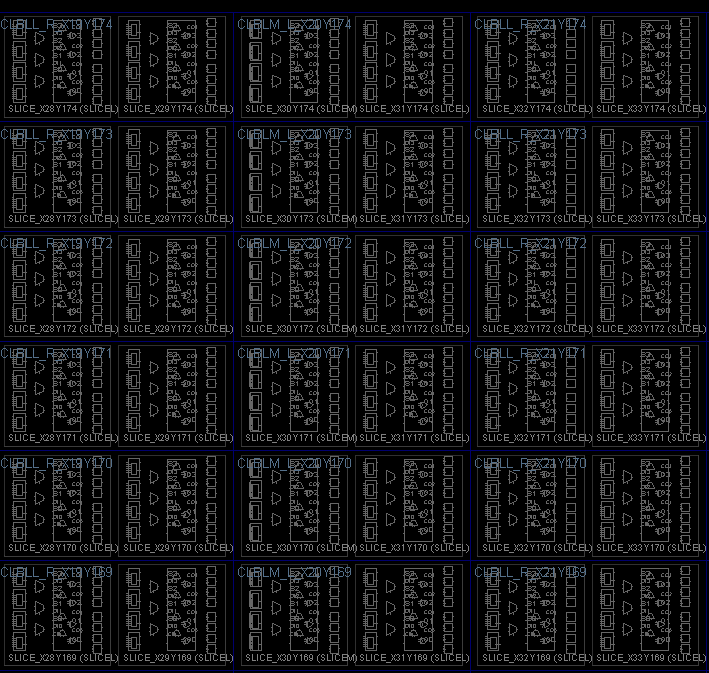

蓝色框中的就是CLB,同时也可以发现,CLB是由两个不的元素组成,这个元素我们称之为SLICE。

如果把FPGA实现的电路看做是积木拼成的摩天大楼,那么CLB就是实现大楼的最基本元素--砖块。 但是我们盖楼不可能只使用一种砖块,同样的为了实现各种功能的电路,我们也要把CLB切成了更小的块以便灵活组合实现更复杂的电路。

所以,CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。有了这四种基本元素后,我们就可以灵活组合实现各种时序逻辑和组合逻辑了。

一个CLB是由2个SLICE组成的,SLICE根据其中的LUT6能实现的功能可以分为以下两种:

CLB的组成可以是上图的1个SLICEM + 1个SLICEL,或者是2个SLICEL,但是不会是2个SLICEM 。一般情况下,CLB中比例SLICEL:SLICEM = 2:1。

总结一下:1个CLB = 2个SLICE = 2 ×(4个LUT + 3个MUX + 1个CARRY4 + 8个FF),这就是CLB和SLICE的架构了。

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----LUT查找表

查找表Look-up Table,本质上就是1个6输入,64深度的ROM(SLICEM中的则是RAM,因为可读)。通过将所有结果保存在其内部,使用时通过由输入构建的地址线对其进行查找,从而实现6输入的函数逻辑。

比如,你要实现功能:y = a | b ^ c & d & e & f。输入一共6个,可能的结果就是2的6次方64个,我把这64个结果全部存到LUT里,只要在使用的时候根据输入(也就是地址),拿出存在对应位置的结果就行了,这就是LUT实现各种函数的原理。

需要注意的是SLICEM中的查找表,除了读功能外还具备写功能,这就使得其内部的LUT由一个ROM变成了一个RAM,这也是其实现移位寄存器功能和分布式DRAM功能的原因。

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----移位寄存器

SLICEM可以在不使用触发器的条件下配置为32位移位寄存器(注意:只能左移)。这样,每个LUT可以将串行数据延迟1到32个时钟周期。移位输入D(LUT DI1脚)和移位输出Q31(LUT MC31脚)可以进行级联,以形成更大的移位寄存器。一个SLICEM的4个LUT6级联可以实现128个时钟周期的延时。多个SLICEM也可以进行组合。但SLICEM之间没有直接连接以形成更长的移位寄存器,在LUT B/C/D处的MC31输出也没有。由此产生的可编程延迟可用于平衡数据pipeline的时间。

那这种 Shifter Register 可以用来做什么呢?Xilinx Guide 中也给出了回答:

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----分布式RAM(DRAM,Distributed RAM)

SLICEM 中的 LUT 除了用作移位寄存器外,还可以被配置为Distributed RAM(DRAM)。DRAM 的 write 是同步的,read 则是异步的。注意这里所说的同步异步不是跨时钟域的概念,而是类似于组合逻辑和时序逻辑的概念。可以理解为,write 是时序逻辑,只有在时钟有效沿且 write enable 为1时,数据才会被写入。而 read 则和时钟无关,只要地址有效,数据就会在当前周期输出。如果想要同步输出,我们可以自己在输出端加 register。

DRAM的概念是相对于BRAM来说的,BRAM是FPGA底层的固有的硬件单元,而DRAM则是使用LUT配置而成的,其位置和使用会稍微灵活一些,但是也有其他不足,两者的使用需要权衡。

DRAM可以分为以下几种:

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----MUX多路选择器(Multiplexer)

多路选择器MUX是一个多输入、单输出的组合逻辑电路,一个n输入的多路选择器就是一个n路的数字开关,可以根据通道选择控制信号的不同,从n个输入中选取一个输出到公共的输出端。

在FPGA底层,MUX也是作为一种基本的逻辑单元而存在,每一个SLICE中有3个MUX:2个F7MUX(F7AMUX + F7BMUX) + 1个F8MUX,这三个MUX本质上都是一个2选一的多路选择器,其都是作为LUT的辅助而存在。

每个SLICE中都有2个MUXF7,其输入只能为LUT6的输出,而输出只能接到MUXF8;每个SLICE中都有1个MUXF8,其输入只能为MUXF7的输出。

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----存储单元之触发器、寄存器与锁存器

Slice中的存储单元便是我们前面提到的寄存器FF,FF是实现时序逻辑最基本的单元。需要注意的是,这些FF中的一半还可以被配置为锁存器Latch,但是一旦被配置后,则剩余的一半FF就不能使用了,会造成一定的资源浪费。

FF可以通过不同的控制集(时钟使能、复位方式、复位电平)来配置成不同形式的寄存器:

本章节只是大概阐述,详细内容强烈推荐阅读:从底层结构开始学习FPGA----进位链CARRY4

CARRY4是一种超前进位的加法器(或者说减法器),是FPGA内部用来实现加减法运算的基本运算单元,但同时也可以实现一些其他的函数功能。每个CLB Slice都有一个专用的加法器CARRY4,可以实现两个4bit数的加减法运算。

我想将html转换为纯文本。不过,我不想只删除标签,我想智能地保留尽可能多的格式。为插入换行符标签,检测段落并格式化它们等。输入非常简单,通常是格式良好的html(不是整个文档,只是一堆内容,通常没有anchor或图像)。我可以将几个正则表达式放在一起,让我达到80%,但我认为可能有一些现有的解决方案更智能。 最佳答案 首先,不要尝试为此使用正则表达式。很有可能你会想出一个脆弱/脆弱的解决方案,它会随着HTML的变化而崩溃,或者很难管理和维护。您可以使用Nokogiri快速解析HTML并提取文本:require'nokogiri'h

我有一个在Linux服务器上运行的ruby脚本。它不使用rails或任何东西。它基本上是一个命令行ruby脚本,可以像这样传递参数:./ruby_script.rbarg1arg2如何将参数抽象到配置文件(例如yaml文件或其他文件)中?您能否举例说明如何做到这一点?提前谢谢你。 最佳答案 首先,您可以运行一个写入YAML配置文件的独立脚本:require"yaml"File.write("path_to_yaml_file",[arg1,arg2].to_yaml)然后,在您的应用中阅读它:require"yaml"arg

我已经在Sinatra上创建了应用程序,它代表了一个简单的API。我想在生产和开发上进行部署。我想在部署时选择,是开发还是生产,一些方法的逻辑应该改变,这取决于部署类型。是否有任何想法,如何完成以及解决此问题的一些示例。例子:我有代码get'/api/test'doreturn"Itisdev"end但是在部署到生产环境之后我想在运行/api/test之后看到ItisPROD如何实现? 最佳答案 根据SinatraDocumentation:EnvironmentscanbesetthroughtheRACK_ENVenvironm

给定一个复杂的对象层次结构,幸运的是它不包含循环引用,我如何实现支持各种格式的序列化?我不是来讨论实际实现的。相反,我正在寻找可能会派上用场的设计模式提示。更准确地说:我正在使用Ruby,我想解析XML和JSON数据以构建复杂的对象层次结构。此外,应该可以将该层次结构序列化为JSON、XML和可能的HTML。我可以为此使用Builder模式吗?在任何提到的情况下,我都有某种结构化数据-无论是在内存中还是文本中-我想用它来构建其他东西。我认为将序列化逻辑与实际业务逻辑分开会很好,这样我以后就可以轻松支持多种XML格式。 最佳答案 我最

我只想对我一直在思考的这个问题有其他意见,例如我有classuser_controller和classuserclassUserattr_accessor:name,:usernameendclassUserController//dosomethingaboutanythingaboutusersend问题是我的User类中是否应该有逻辑user=User.newuser.do_something(user1)oritshouldbeuser_controller=UserController.newuser_controller.do_something(user1,user2)我

之前在培训新生的时候,windows环境下配置opencv环境一直教的都是网上主流的vsstudio配置属性表,但是这个似乎对新生来说难度略高(虽然个人觉得完全是他们自己的问题),加之暑假之后对cmake实在是爱不释手,且这样配置确实十分简单(其实都不需要配置),故斗胆妄言vscode下配置CV之法。其实极为简单,图比较多所以很长。如果你看此文还配不好,你应该思考一下是不是自己的问题。闲话少说,直接开始。0.CMkae简介有的人到大二了都不知道cmake是什么,我不说是谁。CMake是一个开源免费并且跨平台的构建工具,可以用简单的语句来描述所有平台的编译过程。它能够根据当前所在平台输出对应的m

这篇文章是继上一篇文章“Observability:从零开始创建Java微服务并监控它(一)”的续篇。在上一篇文章中,我们讲述了如何创建一个Javaweb应用,并使用Filebeat来收集应用所生成的日志。在今天的文章中,我来详述如何收集应用的指标,使用APM来监控应用并监督web服务的在线情况。源码可以在地址 https://github.com/liu-xiao-guo/java_observability 进行下载。摄入指标指标被视为可以随时更改的时间点值。当前请求的数量可以改变任何毫秒。你可能有1000个请求的峰值,然后一切都回到一个请求。这也意味着这些指标可能不准确,你还想提取最小/

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

最近在学习CAN,记录一下,也供大家参考交流。推荐几个我觉得很好的CAN学习,本文也是在看了他们的好文之后做的笔记首先是瑞萨的CAN入门,真的通透;秀!靠这篇我竟然2天理解了CAN协议!实战STM32F4CAN!原文链接:https://blog.csdn.net/XiaoXiaoPengBo/article/details/116206252CAN详解(小白教程)原文链接:https://blog.csdn.net/xwwwj/article/details/105372234一篇易懂的CAN通讯协议指南1一篇易懂的CAN通讯协议指南1-知乎(zhihu.com)视频推荐CAN总线个人知识总

深度学习部署:Windows安装pycocotools报错解决方法1.pycocotools库的简介2.pycocotools安装的坑3.解决办法更多Ai资讯:公主号AiCharm本系列是作者在跑一些深度学习实例时,遇到的各种各样的问题及解决办法,希望能够帮助到大家。ERROR:Commanderroredoutwithexitstatus1:'D:\Anaconda3\python.exe'-u-c'importsys,setuptools,tokenize;sys.argv[0]='"'"'C:\\Users\\46653\\AppData\\Local\\Temp\\pip-instal