目录

寄存器是模块之间信息交互的窗口,可以通过配置寄存器,使寄存器工作在一定状态下,也可以通过读寄存器来获取当前的工作状态。原来对DUT进行读写操作需要启动sequence并制定寄存器发送来的地址,将transaction发送到dut一侧。

通过建立寄存器模型后,用uvm_reg内置的方法如write()、read()对对应寄存器进行访问会变得更轻松,同时通过后门访问不耗时的方法也可以更快的获得DUT一侧寄存器的信息。同时内建的sequence也可以更快完成项目初期基本功能的检验。

uvm_reg_filed: 用来针对寄存器功能域来构建对应的比特位,寄存器模型中的最小单位。

uvm_reg:与寄存器相匹配,内部可以例化和配置多个uvm_reg_filed。

uvm_reg_block: 可以容纳多个uvm_reg、uvm_men、uvm_reg_map。一个寄存器模型至少包含一个uvm_reg_block。

uvm_reg_map :用于储存各个寄存器地址和访问属性,将这些地址转化为可以访问的物理地址。

uvm_mem :对应硬件的储存模型。

1. 声明各个寄存器,并对寄存器中各个域进行build和configure。

2. 在uvm_reg_block中声明各个寄存器,添加uvm_reg_map。

3. 在uvm_reg_block的build函数中例化配置并调用各个寄存器的build函数。

4. uvm_reg_map 例化,并将各个寄存器加入到uvm_reg_map中。

5. lock_model,防止外部的修改。

示例:

class WDOGLOAD_reg extends uvm_reg; //寄存器继承于uvm_reg

`uvm_object_utils(WDOGLOAD_reg)

rand uvm_reg_field LOADVAL; //声明域

function new(string name = "WDOGLOAD_reg");

//name,parameterm,has_coverage, 宽度指的是寄存器总共的宽度

super.new(name, 32, UVM_CVR_ALL);

endfunction

virtual function void build(); //build函数,需要手动允许,用于域的配置

LOADVAL = uvm_reg_field::type_id::create("LOADVAL"); //例化

/*配置域;1-域在哪个寄存器;2-域的宽度;3-最低位;4-存取方式;5-是否易失;

6-复位值;7-是否有复位;8-是否可以随机化;9-是否可以单独存取*/

LOADVAL.configure(this, 32, 0, "RW", 0, 'hFFFFFFFF, 1, 0, 0);

endfunction

endclass

class rkv_watchdog_rgm extends uvm_reg_block; //寄存器模型继承与uvm_reg_block

`uvm_object_utils(rkv_watchdog_rgm)

rand WDOGLOAD_reg WDOGLOAD; //声明寄存器模型为rand

uvm_reg_map map; //声明map

function new(string name = "rkv_watchdog_rgm");

super.new(name, UVM_NO_COVERAGE);

endfunction

virtual function void build();

WDOGLOAD = WDOGLOAD_reg::type_id::create("WDOGLOAD"); //实例化reg

WDOGLOAD.configure(this); //指定后门访问的路径

WDOGLOAD.build(); //调用build函数

//实例化map;1-名称;2-基地址;3-系统总线宽度,byte;4-大小端;5-能否以byte寻址

map = create_map("map", 'h0, 4, UVM_LITTLE_ENDIAN,0);

//将寄存器加入map;1-要加入的寄存器;2-寄存器的地址;3-寄存器的存取方式

map.add_reg(WDOGLOAD, 32'h000, "RW");

lock_model(); //防止外部对寄存器模型的修改

endfunction

endclass在创建了寄存器模型后,需要将寄存器模型集成。一个正常的寄存器模型集成通常由包括adapter、predictor的创建和连接。

uvm_reg_adapter的出现是为了解决寄存器模型一侧和总线一侧数据类型不同,需要进行数据类型的转化。

当用寄存器模型进行前门读写时寄存器模型通过sequence都会产生一个名为uvm_reg_bus_op变量,该变量储存着读写类型以及操作地址,需要通过adapter函数reg2bus以及bus2reg桥接sequencer和rgm一侧,对变量进行类型转化。

uvm_reg_bus_op 源代码:

typedef struct {

// Variable: kind

//

// Kind of access: READ or WRITE.

//

uvm_access_e kind;

// Variable: addr

//

// The bus address.

//

uvm_reg_addr_t addr;

// Variable: data

//

// The data to write. If the bus width is smaller than the register or

// memory width, ~data~ represents only the portion of ~value~ that is

// being transferred this bus cycle.

//

uvm_reg_data_t data;

// Variable: n_bits

//

// The number of bits of <uvm_reg_item::value> being transferred by

// this transaction.

int n_bits;

/*

constraint valid_n_bits {

n_bits > 0;

n_bits <= `UVM_REG_DATA_WIDTH;

}

*/

// Variable: byte_en

//

// Enables for the byte lanes on the bus. Meaningful only when the

// bus supports byte enables and the operation originates from a field

// write/read.

//

uvm_reg_byte_en_t byte_en;

// Variable: status

//

// The result of the transaction: UVM_IS_OK, UVM_HAS_X, UVM_NOT_OK.

// See <uvm_status_e>.

//

uvm_status_e status;

} uvm_reg_bus_op;reg2bus以及bus2reg:

class rkv_watchdog_reg_adapter extends uvm_reg_adapter;

`uvm_object_utils(rkv_watchdog_reg_adapter) //object类型

function new(string name = "rkv_watchdog_reg_adapter");

super.new(name);

provides_responses = 1; //如果总线返回rsp,应当使能provides_responses

endfunction

function uvm_sequence_item reg2bus(const ref uvm_reg_bus_op rw);

apb_transfer t = apb_transfer::type_id::create("t");

t.trans_kind = (rw.kind == UVM_WRITE) ? WRITE : READ;

t.addr = rw.addr;

t.data = rw.data;

t.idle_cycles = 1;

return t;

endfunction

function void bus2reg(uvm_sequence_item bus_item, ref uvm_reg_bus_op rw);

apb_transfer t;

if (!$cast(t, bus_item)) begin

`uvm_fatal("CASTFAIL","Provided bus_item is not of the correct type")

return;

end

rw.kind = (t.trans_kind == WRITE) ? UVM_WRITE : UVM_READ;

rw.addr = t.addr;

rw.data = t.data;

rw.status = UVM_IS_OK;

endfunction

endclassadapter的创建与连接:

class rkv_watchdog_env extends uvm_env;

……

function void build_phase(uvm_phase phase);

super.build_phase(phase);

if(!uvm_config_db#(rkv_watchdog_rgm)::get(this,"","rgm", rgm)) begin //rgm一般在test例化

rgm = rkv_watchdog_rgm::type_id::create("rgm", this);

rgm.build();

end

adapter = rkv_watchdog_reg_adapter::type_id::create("adapter", this); //在env例化

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

rgm.map.set_sequencer(apb_mst.sequencer, adapter); //adapter的连接

endfunction

……

endclass

寄存器模型访问方式可以分为前门访问和后门访问。

前门方法就是通过在寄存器模型上配置总线,来实现总线上物理时序的访问。

后门访问是利用UVM_DPI将寄存器模型的操作直接作用于DUT内的寄存器变量而不通过物理总线访问。从广义上来将,所有不通过DUT的总线而对DUT内部的寄存器或者存储器进行存取的操作都是后门访问的操作。

后门访问步骤:

1. 设置每个寄存器的后门访问路径。

2. 设置好根路径。

// block一侧设置后门访问路径

class reg_block extends uvm_reg_block;

······

invert.configure(this, null, "invert");

endclass

//test一侧设置绝对路径

function void base_test::build_phase(uvm_phase phase);

······

rm.set_hdl_path_root("top_tb.my_dut");

endfunction前门访问和后门访问的区别:

1. 前方访问需要通过总线协议,需要耗时。后门访问通过UVM DPI关联硬件路径,直接读取或修改硬件,不消耗仿时间。

2. 前门访问只能按字读取,无法读取寄存器域,而后门访问可以读取寄存器域。

3. 前门访问可以通过predictor监测总线做预测,而后门访问只能通过auto prediction方式对寄存器内容做预测。

4. 前门访问正确反映了时序关系,可以有效捕捉总线错误,而后方访问不受时序约束,可能会发生时序冲突。

后门访问的优势:

1. 运行时间远小于前门,可以通过后门访问来配置寄存器。

2. 可以给只读寄存器赋初值。

后门访问的劣势:

1. 后门访问不经过总线,无法在波形文件中通过总线变化来观测,增大了观测调试难度。

镜像值(mirror value):DUT一侧寄存器里的值会不断变更,寄存器模型一侧设置了专门用于最大可能与DUT保持同步的值,这个值为镜像值。

期望值(desired value):想要修改DUT一侧寄存器的值。先通过set方法设置期望值,然后通过update方法更新,update方法会检验镜像值和期望值是否一致,若不一致,就将期望值写入DUT中,并更新镜像值。

由于镜像值需要尽可能与DUT保持同步,因此需要对寄存器模型的镜像值进行预测。寄存器模型预测可以分为自动预测(auto prediction)或者通过显示预测(通过predictor进行预测)。

自动预测:自动预测会利用寄存器的操作来自动记录每一次寄存器的读写数值,并在后台自动调用predict方法。

显示预测:通过将predictor集成到环境中,通过monitor监测物理总线,再将监测到的事务传递经adapter转换后传递给寄存器模型并更新信息到map中。

自动预测示例:

rgm.map.set_auto_predict(1)显示预测:

class rkv_watchdog_env extends uvm_env;

……

uvm_reg_predictor #(apb_transfer) predictor; //声明

function void build_phase(uvm_phase phase);

predictor = uvm_reg_predictor#(apb_transfer)::type_id::create("predictor", this);//例化

endfunction

function void connect_phase(uvm_phase phase);

super.connect_phase(phase);

apb_mst.monitor.item_collected_port.connect(predictor.bus_in); //monitor连接到predictor

predictor.map = rgm.map; // map相连

predictor.adapter = adapter; // adapter 相连

endfunction

function void end_of_elaboration_phase(uvm_phase phase);

super.end_of_elaboration_phase(phase);

endfunction

……

endclass

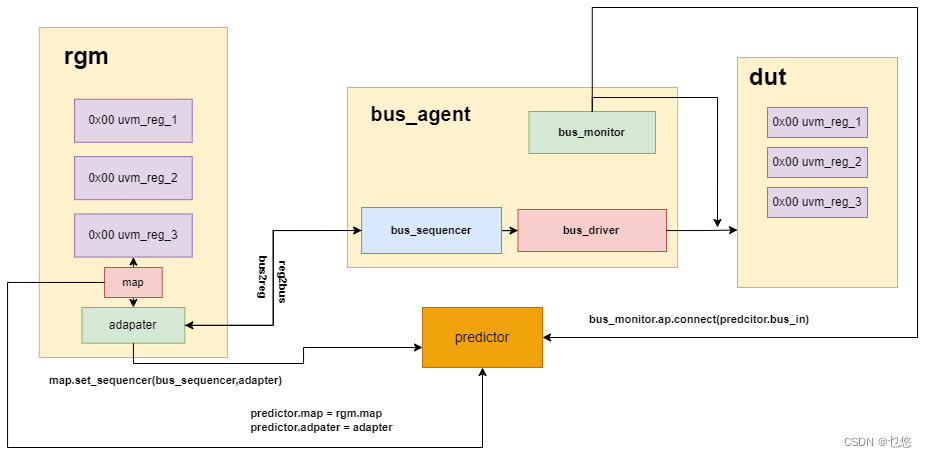

寄存器模型整合如下图所示:

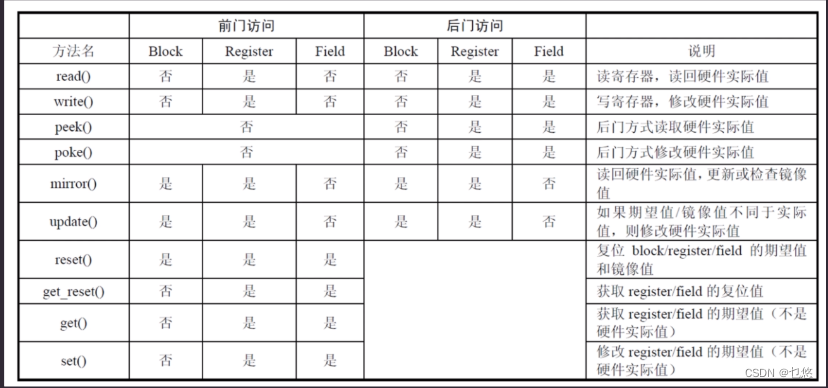

寄存器使模型使用内置的方法来对修改或读取硬件的实际值。

uvm_reg的访问方法由下表所示:

注意:

示例:

rgm.WDOGCONTROL.RESEN.set(1'b1);

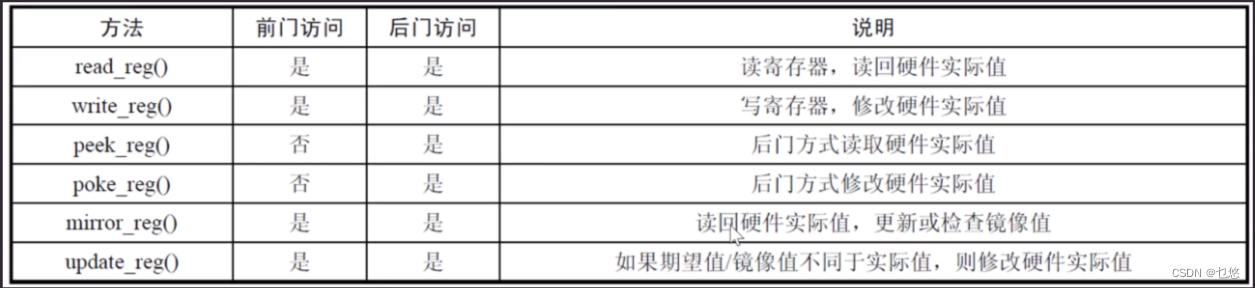

rgm.WDOGCONTROL.update(status); uvm_reg_sequence的方法与uvm_reg类似,如下表所示:

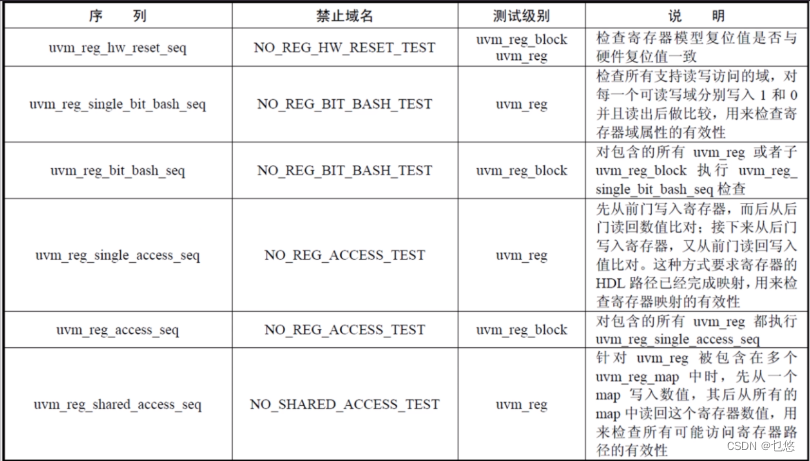

寄存器模型提供了一些内建的sequence,用于项目初期的快速检验,如下表所示:

示例:

class nj_seq extends base_sequence;

……

virtual task body();

uvm_reg_hw_reset_seq reseq;

reseq = new("reseq");

……

reseq.model = rgm; //注意要给model赋值

reseq.start(m_sequencer);

……

endtask

enclass我有一个模型:classItem项目有一个属性“商店”基于存储的值,我希望Item对象对特定方法具有不同的行为。Rails中是否有针对此的通用设计模式?如果方法中没有大的if-else语句,这是如何干净利落地完成的? 最佳答案 通常通过Single-TableInheritance. 关于ruby-on-rails-Rails-子类化模型的设计模式是什么?,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.co

我需要从一个View访问多个模型。以前,我的links_controller仅用于提供以不同方式排序的链接资源。现在我想包括一个部分(我假设)显示按分数排序的顶级用户(@users=User.all.sort_by(&:score))我知道我可以将此代码插入每个链接操作并从View访问它,但这似乎不是“ruby方式”,我将需要在不久的将来访问更多模型。这可能会变得很脏,是否有针对这种情况的任何技术?注意事项:我认为我的应用程序正朝着单一格式和动态页面内容的方向发展,本质上是一个典型的网络应用程序。我知道before_filter但考虑到我希望应用程序进入的方向,这似乎很麻烦。最终从任何

我有一个包含模块的模型。我想在模块中覆盖模型的访问器方法。例如:classBlah这显然行不通。有什么想法可以实现吗? 最佳答案 您的代码看起来是正确的。我们正在毫无困难地使用这个确切的模式。如果我没记错的话,Rails使用#method_missing作为属性setter,因此您的模块将优先,阻止ActiveRecord的setter。如果您正在使用ActiveSupport::Concern(参见thisblogpost),那么您的实例方法需要进入一个特殊的模块:classBlah

我有一个表单,其中有很多字段取自数组(而不是模型或对象)。我如何验证这些字段的存在?solve_problem_pathdo|f|%>... 最佳答案 创建一个简单的类来包装请求参数并使用ActiveModel::Validations。#definedsomewhere,atthesimplest:require'ostruct'classSolvetrue#youcouldevencheckthesolutionwithavalidatorvalidatedoerrors.add(:base,"WRONG!!!")unlesss

我想向我的Controller传递一个参数,它是一个简单的复选框,但我不知道如何在模型的form_for中引入它,这是我的观点:{:id=>'go_finance'}do|f|%>Transferirde:para:Entrada:"input",:placeholder=>"Quantofoiganho?"%>Saída:"output",:placeholder=>"Quantofoigasto?"%>Nota:我想做一个额外的复选框,但我该怎么做,模型中没有一个对象,而是一个要检查的对象,以便在Controller中创建一个ifelse,如果没有检查,请帮助我,非常感谢,谢谢

我有一些非常大的模型,我必须将它们迁移到最新版本的Rails。这些模型有相当多的验证(User有大约50个验证)。是否可以将所有这些验证移动到另一个文件中?说app/models/validations/user_validations.rb。如果可以,有人可以提供示例吗? 最佳答案 您可以为此使用关注点:#app/models/validations/user_validations.rbrequire'active_support/concern'moduleUserValidationsextendActiveSupport:

对于Rails模型,是否可以/建议让一个类的成员不持久保存到数据库中?我想将用户最后选择的类型存储在session变量中。由于我无法从我的模型中设置session变量,我想将值存储在一个“虚拟”类成员中,该成员只是将值传递回Controller。你能有这样的类(class)成员吗? 最佳答案 将非持久属性添加到Rails模型就像任何其他Ruby类一样:classUser扩展解释:在Ruby中,所有实例变量都是私有(private)的,不需要在赋值前定义。attr_accessor创建一个setter和getter方法:classUs

我有一个正在构建的应用程序,我需要一个模型来创建另一个模型的实例。我希望每辆车都有4个轮胎。汽车模型classCar轮胎模型classTire但是,在make_tires内部有一个错误,如果我为Tire尝试它,则没有用于创建或新建的activerecord方法。当我检查轮胎时,它没有这些方法。我该如何补救?错误是这样的:未定义的方法'create'forActiveRecord::AttributeMethods::Serialization::Tire::Module我测试了两个环境:测试和开发,它们都因相同的错误而失败。 最佳答案

ruby如何管理内存。例如:如果我们在执行过程中采用C程序,则以下是内存模型。类似于这个ruby如何处理内存。C:__________________|||stack|||------------------||||------------------|||||Heap|||||__________________|||data|__________________|text|__________________Ruby:? 最佳答案 Ruby中没有“内存”这样的东西。Class#allocate分配一个对象并返回该对象。这就是程序

我正在使用Rails3.1并在一个论坛上工作。我有一个名为Topic的模型,每个模型都有许多Post。当用户创建新主题时,他们也应该创建第一个Post。但是,我不确定如何以相同的形式执行此操作。这是我的代码:classTopic:destroyaccepts_nested_attributes_for:postsvalidates_presence_of:titleendclassPost...但这似乎不起作用。有什么想法吗?谢谢! 最佳答案 @Pablo的回答似乎有你需要的一切。但更具体地说...首先改变你View中的这一行对此#