⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者公众号【AIShareLab】回复 FPGA 也可获取。

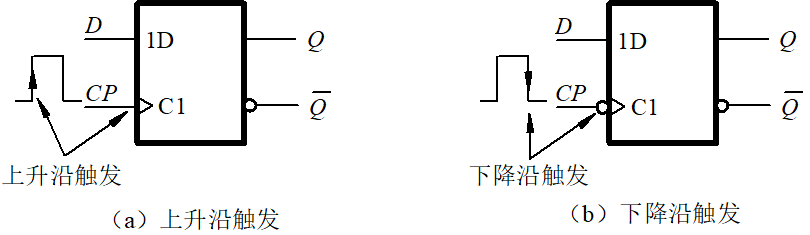

把 CP 有效沿到来之前电路的状态称为现态,用 Q n Q^n Qn表示。

把 CP 有效沿到来之后,电路所进入的新状态称为次态,用 Q n + 1 Q^{n+1} Qn+1表示。

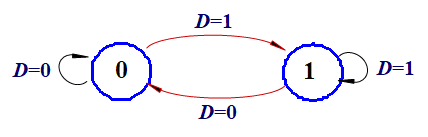

| D | Q n Q^n Qn | Q n + 1 Q^{n+1} Qn+1 |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Q n + 1 = D Q^{n+1} = D Qn+1=D

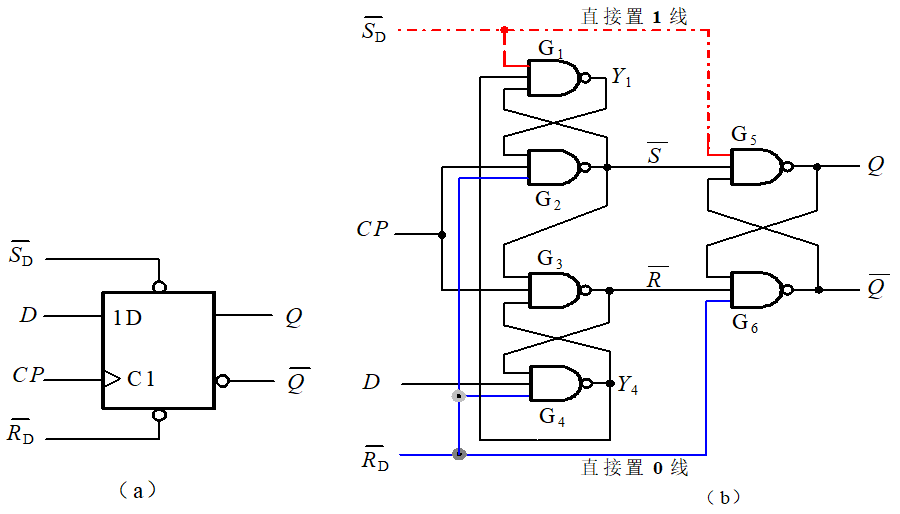

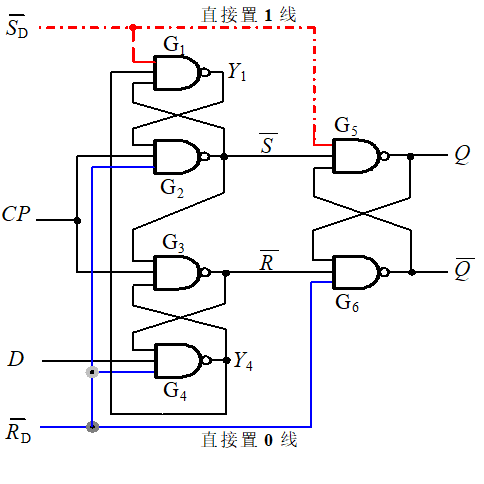

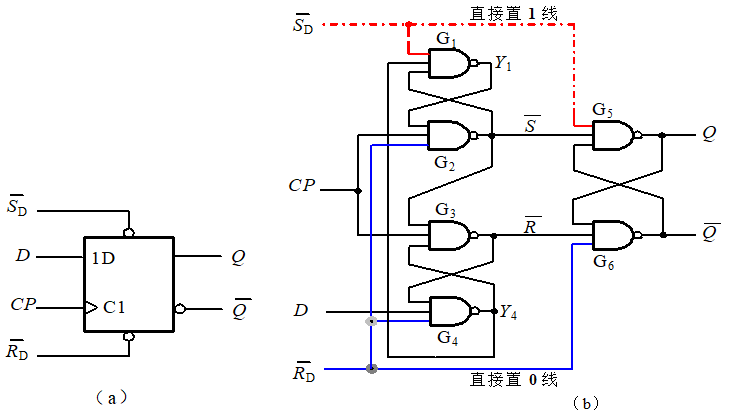

由于直接置1和清零时跟CP信号无关,所以称置1、清零操作是异步置1和异步清零。

直接置1和直接清零的过程如下:

(1) 当 S ˉ D = 0 \bar{S}_{D}=0 SˉD=0, R ˉ D = 1 \bar{R}_{D}=1 RˉD=1 时, 使得 Y 1 = 1 Y_{1}=1 Y1=1 , S ˉ = Y 1 ⋅ C P ⋅ R ˉ D ‾ = C P ‾ \bar{S}=\overline{Y_{1} \cdot C P \cdot \bar{R}_{D}}=\overline{C P} Sˉ=Y1⋅CP⋅RˉD=CP, R ˉ = S ˉ ⋅ C P ⋅ Y 4 ‾ = 1 \quad \bar{R}=\overline{\bar{S} \cdot C P \cdot Y_{4}}=1 Rˉ=Sˉ⋅CP⋅Y4=1 ,于是 Q = 1 Q=1 Q=1, Q ˉ = 0 \bar{Q}=0 Qˉ=0 , 即将输出 Q 直接置 1 。

(2) 当 S ˉ D = 1 \bar{S}_{\mathrm{D}}=1 SˉD=1, R ˉ D = 0 \bar{R}_{\mathrm{D}}=0 RˉD=0 时, 使得 S ˉ = 1 \bar{S}=1 Sˉ=1 , 于是 Q = 0 Q=0 Q=0, Q ˉ = 1 \bar{Q}=1 Qˉ=1 , 即将输出 Q 直接清零。

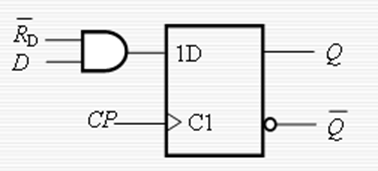

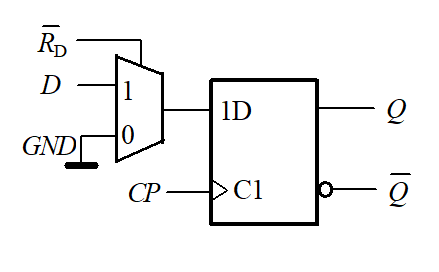

所谓同步清零是指在清零输入信号有效,并且CP的有效边沿(如上升沿)到来时,才能将触发器清零。

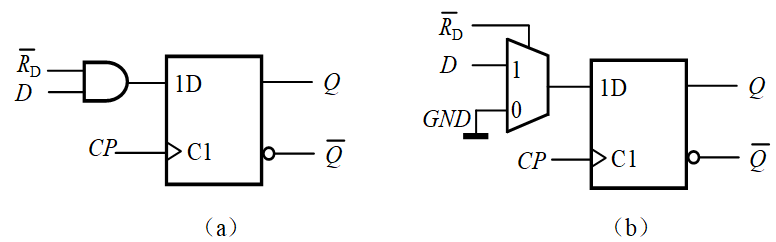

(a) 实现同步清零的方案之一

(b) 实现同步清零的方案之二

功能:

Q

n

+

1

=

C

E

‾

⋅

Q

n

+

C

E

⋅

D

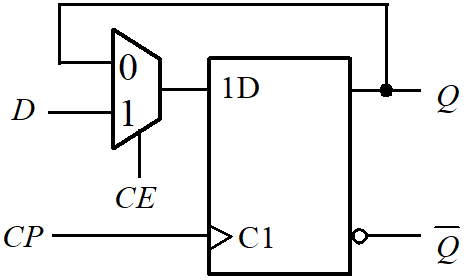

Q^{n+1}=\overline{C E} \cdot Q^{n}+C E \cdot D

Qn+1=CE⋅Qn+CE⋅D

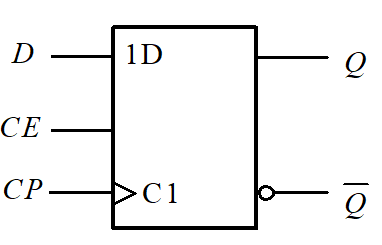

逻辑符号

例1.试对图所示的带有异步清零和异步置位的边沿D触发器进行建模。

有异步输入端的D触发器

//版本1:

module Set_Rst_DFF (Q, Q_, D, CP, Rd_, Sd_);

output Q,Q_;

input D,CP,Rd_,Sd_;

wire Y1,Y2,Y3,Y4,Y5,Y6;

assign #5 Y1 = ~(Sd_ & Y2 & Y4);

assign #5 Y2 = ~(Rd_ & CP & Y1);

assign #5 Y3 = ~(CP & Y2 & Y4);

assign #5 Y4 = ~(Rd_ & Y3 & D );

assign #5 Y5 = ~(Sd_ & Y2 & Y6);

assign #5 Y6 = ~(Rd_ & Y3 & Y5);

assign Q = Y5;

assign Q_= Y6;

endmodule

版本1: 根据该图使用连续赋值语句来建模,在assign语句中的#5表示给每个与非门加5个单位时间的传输延迟。

//版本2

module Set_Rst_DFF_bh (Q, Q_, D, CP, Rd_, Sd_);

output reg Q;

output Q_;

input D,CP,Rd_,Sd_;

assign Q_= ~Q;

always @(posedge CP or negedge Sd_ or negedge Rd_)

if (~Sd_) //等同于: if (Sd_== 0)

Q <= 1'b1;

else if (~Rd_)

Q <= 1'b0;

else

Q <= D;

endmodule

版本2的特点:

采用功能描述风格,使用always和if-else对输出变量赋值。

negedge Sd_是一个异步事件,它与if(~Sd_)必须匹配,negedge Rd_是另一个异步事件,它与if(~Rd_)必须匹配,这是语法规定。

Sd_为0时,将输出Q置1;Sd_=1且Rd_=0时,将输出Q置0;Sd_和Rd_均不为0,且时钟CP的上升沿到来时,将输入D传给输出Q。注意,如果置1事件、置0事件和时钟事件同时发生,则置1事件的优先级别最高、置0事件的次之,时钟事件的优先级最低。

例2 具有同步清零功能的上升沿D触发器。

module Sync_rst_DFF (Q, D, CP, Rd_);

output reg Q;

input D, CP, Rd_;

always @(posedge CP)

if ( !Rd_) // also as (~Rd_)

Q <= 0;

else

Q <= D;

endmodule

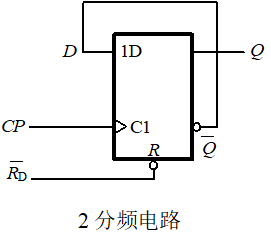

例4 试用功能描述风格对图所示电路进行建模(2分频电路) ,并给出仿真结果。

解:(1)设计块:使用always和if-else语句对输出变量赋值,其代码如下。

`timescale 1 ns/ 1 ns

module _2Divider (Q,CP,Rd_);

output reg Q;

input CP,Rd_;

wire D;

assign D = ~Q;

always @(posedge CP or

negedge Rd_)

if(~Rd_) Q <= 1'b0;

else Q <= D;

endmodule

(2)激励块:给输入变量赋值。

`timescale 1 ns/ 1 ns

module test_2Divider();

reg CP, Rd_; wire Q;

//调用(例化)设计块

_2Divider U1 ( .CP(CP), .Q(Q),.Rd_(Rd_) );

initial begin //产生复位信号Rd_

Rd_ = 1'b0;

Rd_ = #2000 1'b1;

#8000 $stop;

end

always begin //产生时钟信号CP

CP = 1'b0;

CP = #500 1'b1;

#500;

end

endmodule

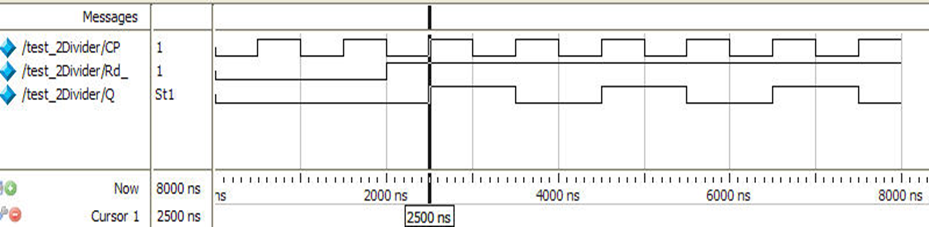

(3)仿真波形(用ModelSim)

由图可知,时钟CP的周期为1000ns,在2000ns之前,清零信号Rd_有效,输出Q被清零。在此之后,Rd_=1,在2500ns时,CP上升沿到来,Q=1;到下一个CP上升沿(3500ns)时,Q=0,再到下一个CP上升沿(4500ns)时,Q=1,……,如此重复,直到8000ns时,系统任务$stop被执行,仿真停止。

总之,在不考虑清零信号Rd_的作用时,每当CP上升沿到来时,触发器状态Q翻转一次。输出信号Q的频率正好是CP频率的二分之一,故称该电路为2分频电路。所谓分频电路,是指可将输入的高频信号变为低频信号输出的电路。

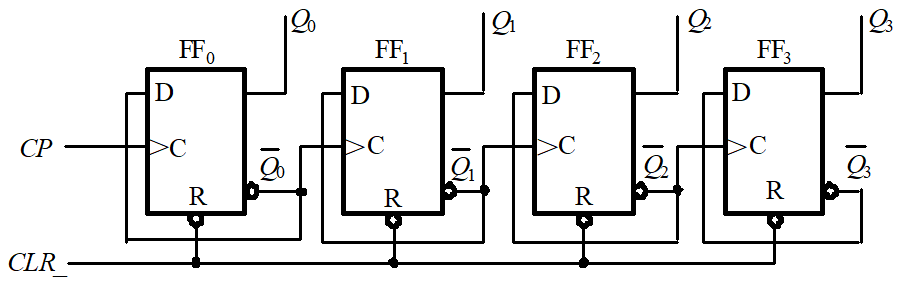

例5 试对图所示电路进行建模,并给出仿真结果。

4位异步二进制计数器逻辑图

解:(1)设计块:采用结构描述风格的代码如下。编写了两个模块,这两个模块可以放在一个文件中,文件名为Ripplecounter.v。

第一个主模块Ripplecounter作为设计的顶层,它实例引用分频器子模块_2Divider1共4次,第二个分频器子模块_2Divider1作为设计的底层。

`timescale 1 ns/ 1 ns

/*==== 设计块:Ripplecounter.v ====*/

module Ripplecounter (Q,CP,CLR_);

output [3:0] Q;

input CP, CLR_;

//实例引用分频器模块 _2Divider1

_2Divider1 FF0 (Q[0],CP ,CLR_);

//注意, 引用时端口的排列顺序--位置关联

_2Divider1 FF1 (Q[1],~Q[0],CLR_);

_2Divider1 FF2 (Q[2],~Q[1],CLR_);

_2Divider1 FF3 (Q[3],~Q[2],CLR_);

endmodule

设计的底层模块 _2Divider1

//分频器子模块

module _2Divider1 (Q,CP,Rd_);

output reg Q;

input CP,Rd_;

always @(posedge CP or negedge Rd_)

if(!Rd_)

Q <= 1'b0;

else

Q <= ~Q;

endmodule

(2)激励块:给输入变量(CLR_和CP)赋值。

/*==== 激励块:test_Ripplecounter.v ====*/

module test_Ripplecounter();

reg CLR_, CP;

wire [3:0] Q;

Ripplecounter i1 (.CLR_(CLR_),.CP(CP),.Q(Q));

initial begin // CLR_

CLR_ = 1'b0;

CLR_ = #20 1'b1;

#400 $stop;

end

always begin // CP

CP = 1'b0;

CP = #10 1'b1;

#10;

end

endmodule

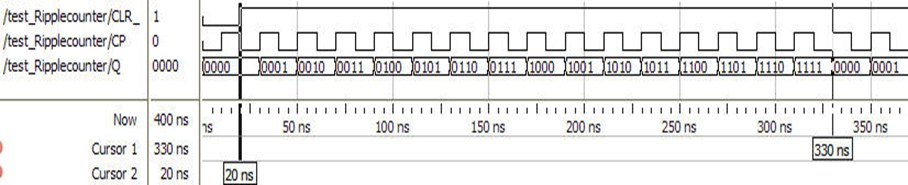

(3)仿真波形:如下图所示。

由图可知,

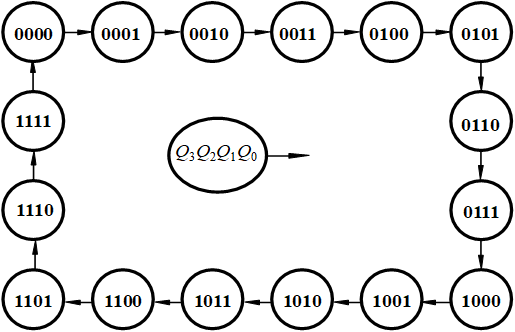

电路首先在CLR_的作用下,输出被清零。此后当CLR_=1时,每当CP上升沿到来时,电路状态Q就在原来二进制值的基础上增加1,即符合二进制递增计数的规律,直到计数值为1111时,再来一个CP上升沿,计数值回到0000,重新开始计数。故称该电路为4位二进制递增计数器(Ripplecounter:纹波计数器) 。

可见,计数器实际上是对时钟脉冲进行计数,每到来一个时钟脉冲触发沿,计数器改变一次状态。

参考文献:

请帮助我理解范围运算符...和..之间的区别,作为Ruby中使用的“触发器”。这是PragmaticProgrammersguidetoRuby中的一个示例:a=(11..20).collect{|i|(i%4==0)..(i%3==0)?i:nil}返回:[nil,12,nil,nil,nil,16,17,18,nil,20]还有:a=(11..20).collect{|i|(i%4==0)...(i%3==0)?i:nil}返回:[nil,12,13,14,15,16,17,18,nil,20] 最佳答案 触发器(又名f/f)是

我正在学习Rails,并阅读了关于乐观锁的内容。我已将类型为integer的lock_version列添加到我的articles表中。但现在每当我第一次尝试更新记录时,我都会收到StaleObjectError异常。这是我的迁移:classAddLockVersionToArticle当我尝试通过Rails控制台更新文章时:article=Article.first=>#我这样做:article.title="newtitle"article.save我明白了:(0.3ms)begintransaction(0.3ms)UPDATE"articles"SET"title"='dwdwd

我有一个rubyonrails应用程序。我按照facebook的说明添加了一个像素。但是,要跟踪转化,Facebook要求您将页面置于达到预期结果时出现的转化中。即,如果我想显示客户已注册,我会将您注册后转到的页面作为成功对象进行跟踪。我的问题是,当客户注册时,在我的应用程序中没有登陆页面。该应用程序将用户带回主页。它在主页上显示了一条消息,所以我想看看是否有一种方法可以跟踪来自Controller操作而不是实际页面的转化。我需要计数的Action没有页面,它们是ControllerAction。是否有任何人都知道的关于如何执行此操作的gem、文档或最佳实践?这是进入布局文件的像素

我有一个super简单的脚本,它几乎包含了FayeWebSocketGitHub页面上用于处理关闭连接的内容:ws=Faye::WebSocket::Client.new(url,nil,:headers=>headers)ws.on:opendo|event|p[:open]#sendpingcommand#sendtestcommand#ws.send({command:'test'}.to_json)endws.on:messagedo|event|#hereistheentrypointfordatacomingfromtheserver.pJSON.parse(event.d

我想写一点“Deprecate-It”库并经常使用“method_added”回调。但是现在我注意到在包含模块时不会触发此回调。是否有任何回调或变通方法,以便在某些内容包含到自身时通知类“Foobar”?用于演示的小Demo:#IncludingModulswon'ttriggermethod_addedcallbackmoduleInvisibleMethoddefinvisible"Youwon'tgetacallbackfromme"endendclassFoobardefself.method_added(m)puts"InstanceMethod:'#{m}'addedto'

一、什么是MQTT协议MessageQueuingTelemetryTransport:消息队列遥测传输协议。是一种基于客户端-服务端的发布/订阅模式。与HTTP一样,基于TCP/IP协议之上的通讯协议,提供有序、无损、双向连接,由IBM(蓝色巨人)发布。原理:(1)MQTT协议身份和消息格式有三种身份:发布者(Publish)、代理(Broker)(服务器)、订阅者(Subscribe)。其中,消息的发布者和订阅者都是客户端,消息代理是服务器,消息发布者可以同时是订阅者。MQTT传输的消息分为:主题(Topic)和负载(payload)两部分Topic,可以理解为消息的类型,订阅者订阅(Su

TCL脚本语言简介•TCL(ToolCommandLanguage)是一种解释执行的脚本语言(ScriptingLanguage),它提供了通用的编程能力:支持变量、过程和控制结构;同时TCL还拥有一个功能强大的固有的核心命令集。TCL经常被用于快速原型开发,脚本编程,GUI和测试等方面。•实际上包含了两个部分:一个语言和一个库。首先,Tcl是一种简单的脚本语言,主要使用于发布命令给一些互交程序如文本编辑器、调试器和shell。由于TCL的解释器是用C\C++语言的过程库实现的,因此在某种意义上我们又可以把TCL看作C库,这个库中有丰富的用于扩展TCL命令的C\C++过程和函数,所以,Tcl是

我看到有关未找到文件min.map的错误消息:GETjQuery'sjquery-1.10.2.min.mapistriggeringa404(NotFound)截图这是从哪里来的? 最佳答案 如果ChromeDevTools报告.map文件的404(可能是jquery-1.10.2.min.map、jquery.min.map或jquery-2.0.3.min.map,但任何事情都可能发生)首先要知道的是,这仅在使用DevTools时才会请求。您的用户不会遇到此404。现在您可以修复此问题或禁用sourcemap功能。修复:获取文

开门见山|拉取镜像dockerpullelasticsearch:7.16.1|配置存放的目录#存放配置文件的文件夹mkdir-p/opt/docker/elasticsearch/node-1/config#存放数据的文件夹mkdir-p/opt/docker/elasticsearch/node-1/data#存放运行日志的文件夹mkdir-p/opt/docker/elasticsearch/node-1/log#存放IK分词插件的文件夹mkdir-p/opt/docker/elasticsearch/node-1/plugins若你使用了moba,直接右键新建即可如上图所示依次类推创建

文章目录概念索引相关操作创建索引更新副本查看索引删除索引索引的打开与关闭收缩索引索引别名查询索引别名文档相关操作新建文档查询文档更新文档删除文档映射相关操作查询文档映射创建静态映射创建索引并添加映射概念es中有三个概念要清楚,分别为索引、映射和文档(不用死记硬背,大概有个印象就可以)索引可理解为MySQL数据库;映射可理解为MySQL的表结构;文档可理解为MySQL表中的每行数据静态映射和动态映射上面已经介绍了,映射可理解为MySQL的表结构,在MySQL中,向表中插入数据是需要先创建表结构的;但在es中不必这样,可以直接插入文档,es可以根据插入的文档(数据),动态的创建映射(表结构),这就