xilinx 7系列FPGA的SelectIO。所谓SelectIO,就是I/O接口以及I/O逻辑的总称;说到I/O,咱们必须先提到FPGA的BANK。在7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。

1.HP BANK只能支持小于等于1.8V电平标准的I/O信号,HP BANK专为高速I/O信号设计,支持DCI(数控阻抗);

HP BANK涉及的高速I/O接口类型:GTX、GTH、GTY、GTP、GTZ、GTM;

他们都是高速收发器,只是传输速率不同,速率大小为:

GTP < GPX < GTH < GTZ < GTY < GTM

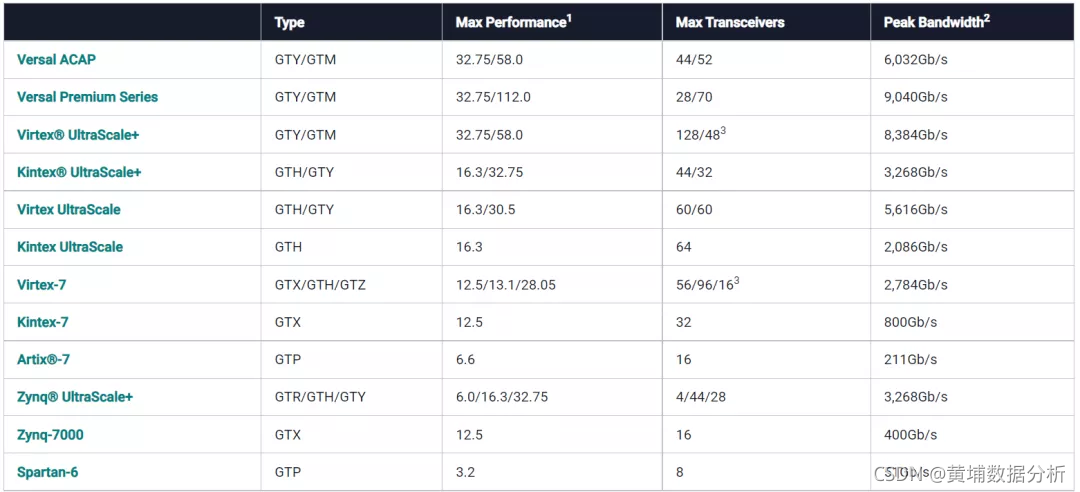

不同芯片上使用的高速收发器也不同,而且同样是GTX,不同系列芯片上的速率也可能不同。

比如7系列的FPGA,GTP最高可以达到6.6Gb/s,GTX最高12.5Gb/s,GTH最高13.1Gb/s,GTZ最高28.05Gb/s

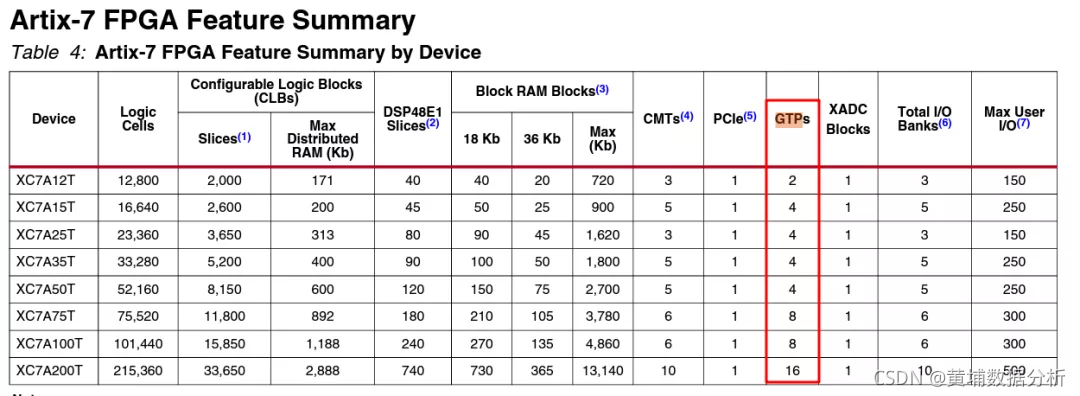

在A7系列上面使用的高速收发器是GTP:

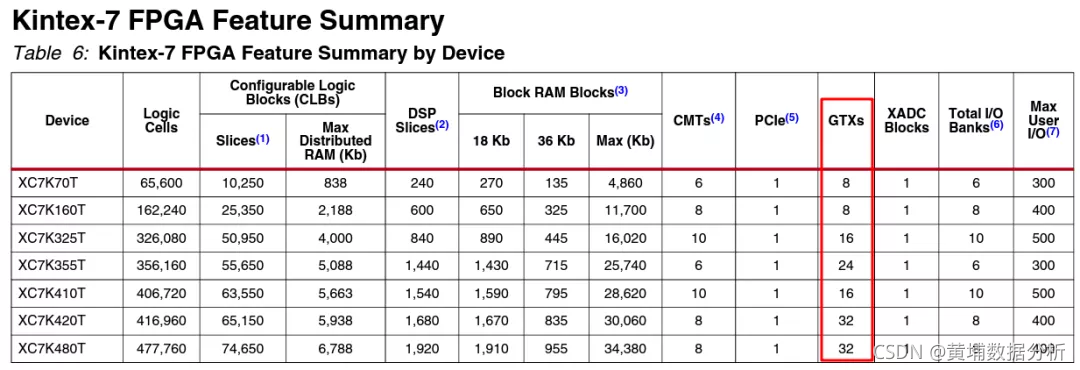

在K7系列上面使用的高速收发器是GTX:

V7系列上面则是GTX/GTH/GTZ都有使用,而且只有在高端的芯片上才使用了GTZ。

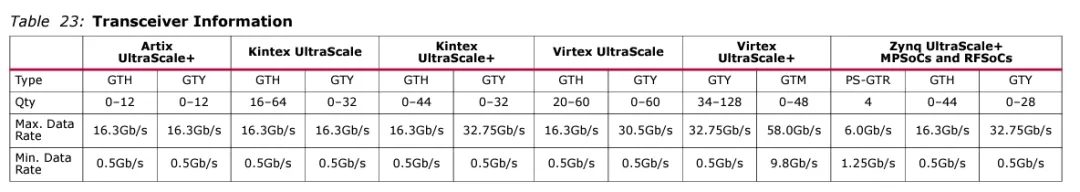

UltraScale和UltraScale+的FPGA,高速收发器使用情况如下表,速度最低的也是GTH,高端的Virtex UltraScale+中使用了GTM

Versal ACAP系列的芯片,使用的也是高端的GTY和GTM

下面的表总结了各系列FPGA的高速收发器的类型和性能。

2.HR BANK则支持小于等于3.3V电平标准的I/O信号,而HR BANK则适合更大众化的所有I/O信号设计。下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

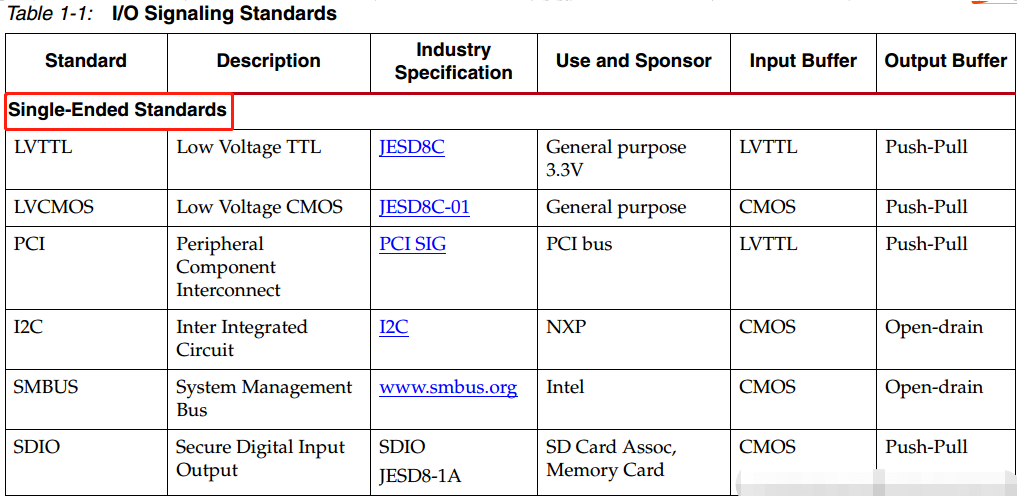

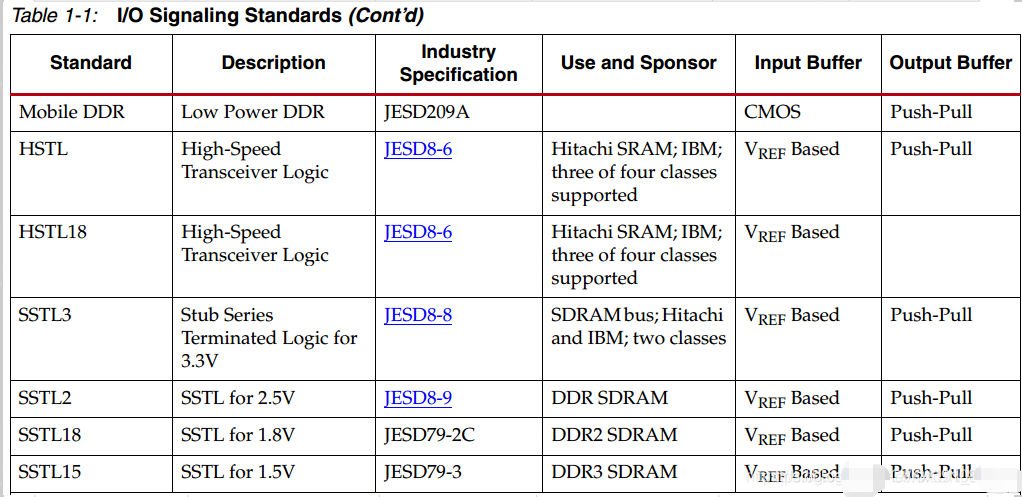

单端的I/O管脚支持LVTTL、LVCMOS、HSTL、PCI等等常用的电平标准。差分的I/O管脚则支持LVDS、差分HSTL等差分信号

Xilinx FPGA提供和支持高性能、可配置、多样化的接口标准。

I/O主要的可配置属性如下:

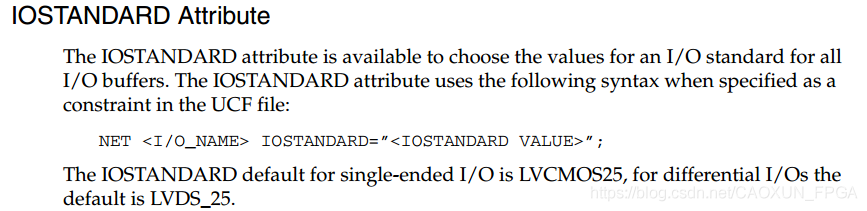

常见IO接口可分为单端IO接口和差分IO接口,详细的IO标准参见下图1,表1

图1:IO接口标准

具体与FPGA管脚(单端、差分)的连接应用可参考该篇博客;

注明:压摆率越快,电平转换时间越短,时间性能越优;

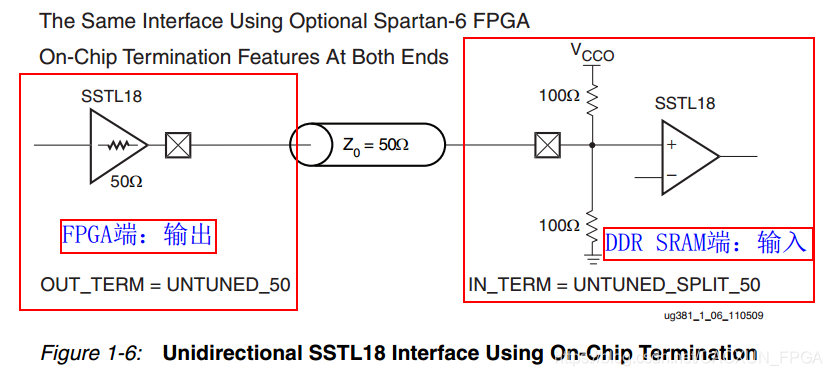

当使用高速IO接口时,在接收端通常需要匹配的端接电阻,有利于高低电平的转换和提高信号的完整性,且端接电阻尽可能的放置在接收端。

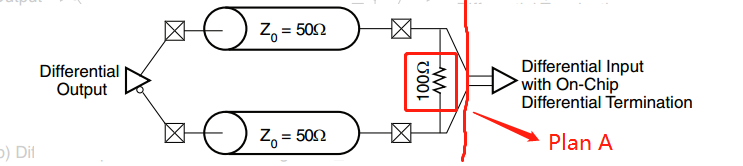

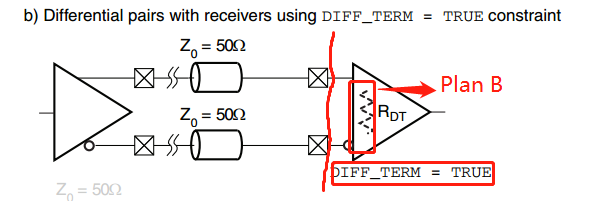

通常需要在差分输入端并行端接100Ω的电阻,FPGA在差分输入接收器提前内置了端接电阻,其阻值R为100Ω,为可选项optional。设计者也可以采用外接端接电阻来进行电阻匹配,阻值选择更灵活。采用片上内置的端接电阻可以节省无聊和缩小PCB面积

通过UCF文件进行约束,是否使用差分输入端接电阻,语法规则如下:

NET <I/O_NAME> DIFF_TERM = "<TRUE/FALSE>"

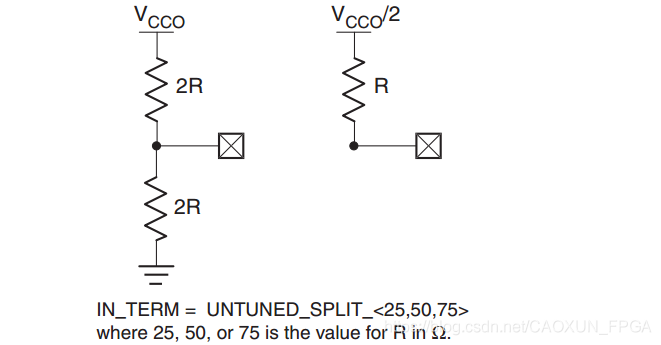

通过UCF文件进行约束,是否使用输入端接电阻,语法规则如下:

NET <I/O_NAME> IN_TERM = "UNTUNED_SPLIT_<25,50,75>"

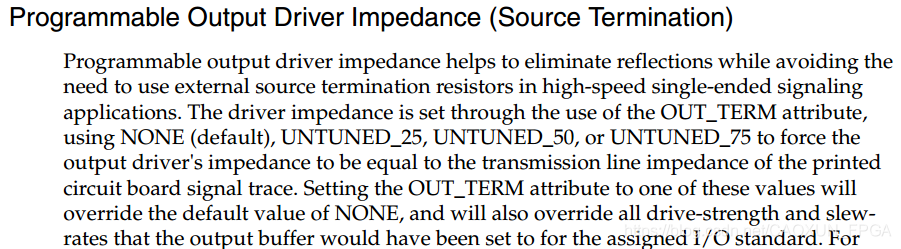

由上图可知,输出端(也称为源端)也可以配置输出端接电阻,以减少信号的反射,应用在高速单端信号场合,例如FPGA输出驱动DDR3芯片。输出端接电阻也是optional可选项,常见阻值R为none,25Ω,50Ω,75Ω。通过UCF文件进行约束,是否使用单端输出端接电阻,语法规则如下:

NET <NET NAME> OUT_TERM = <NONE/ UNTUNED_25 / UNTUNED_50 / UNTUNED_75>;

具体在FPGA中使用时,我们在FPGA约束文件XDC需要对FPGA的管脚做如下处理:

OUTPUT管脚配置:

1.I/O std:

2.output strength

3.slew rate

4.Package-PIN

5.offchip_Term:out_term

INPUT管脚配置:

1.I/O std:

2.Package-PIN

3.offchip_Term(选配):in_term

常见IO接口标准之FPGA_CAOXUN_FPGA的博客-CSDN博客_fpga io口

关于高速接口:LVPECL, LVDS, HSTL, and CML的定义以及端接匹配可参考TI的官方设计指导

下载地址如下:

1.LVPECL、VML、CML、LVDS接口定义介绍-其它文档类资源-CSDN下载

2.TI官方指导LVPECL、LVDS、HSTL、AndCML接口AC耦合匹配教程-其它文档类资源-CSDN下载

或者参考以下教程:

这里有一个很好的答案解释了如何在Ruby中下载文件而不将其加载到内存中:https://stackoverflow.com/a/29743394/4852737require'open-uri'download=open('http://example.com/image.png')IO.copy_stream(download,'~/image.png')我如何验证下载文件的IO.copy_stream调用是否真的成功——这意味着下载的文件与我打算下载的文件完全相同,而不是下载一半的损坏文件?documentation说IO.copy_stream返回它复制的字节数,但是当我还没有下

我正在尝试解析一个文本文件,该文件每行包含可变数量的单词和数字,如下所示:foo4.500bar3.001.33foobar如何读取由空格而不是换行符分隔的文件?有什么方法可以设置File("file.txt").foreach方法以使用空格而不是换行符作为分隔符? 最佳答案 接受的答案将slurp文件,这可能是大文本文件的问题。更好的解决方案是IO.foreach.它是惯用的,将按字符流式传输文件:File.foreach(filename,""){|string|putsstring}包含“thisisanexample”结果的

我想使用spawn(针对多个并发子进程)在Ruby中执行一个外部进程,并将标准输出或标准错误收集到一个字符串中,其方式类似于使用Python的子进程Popen.communicate()可以完成的操作。我尝试将:out/:err重定向到一个新的StringIO对象,但这会生成一个ArgumentError,并且临时重新定义$stdxxx会混淆子进程的输出。 最佳答案 如果你不喜欢popen,这是我的方法:r,w=IO.pipepid=Process.spawn(command,:out=>w,:err=>[:child,:out])

我正在尝试找到一种方法来规范化字符串以将其作为文件名传递。到目前为止我有这个:my_string.mb_chars.normalize(:kd).gsub(/[^\x00-\x7F]/n,'').downcase.gsub(/[^a-z]/,'_')但第一个问题:-字符。我猜这个方法还有更多问题。我不控制名称,名称字符串可以有重音符、空格和特殊字符。我想删除所有这些,用相应的字母('é'=>'e')替换重音符号,并将其余的替换为'_'字符。名字是这样的:“Prélèvements-常规”“健康证”...我希望它们像一个没有空格/特殊字符的文件名:“prelevements_routin

1.错误信息:Errorresponsefromdaemon:Gethttps://registry-1.docker.io/v2/:net/http:requestcanceledwhilewaitingforconnection(Client.Timeoutexceededwhileawaitingheaders)或者:Errorresponsefromdaemon:Gethttps://registry-1.docker.io/v2/:net/http:TLShandshaketimeout2.报错原因:docker使用的镜像网址默认为国外,下载容易超时,需要修改成国内镜像地址(首先阿里

1.postman介绍Postman一款非常流行的API调试工具。其实,开发人员用的更多。因为测试人员做接口测试会有更多选择,例如Jmeter、soapUI等。不过,对于开发过程中去调试接口,Postman确实足够的简单方便,而且功能强大。2.下载安装官网地址:https://www.postman.com/下载完成后双击安装吧,安装过程极其简单,无需任何操作3.使用教程这里以百度为例,工具使用简单,填写URL地址即可发送请求,在下方查看响应结果和响应状态码常用方法都有支持请求方法:getpostputdeleteGet、Post、Put与Delete的作用get:请求方法一般是用于数据查询,

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

SPI接收数据左移一位问题目录SPI接收数据左移一位问题一、问题描述二、问题分析三、探究原理四、经验总结最近在工作在学习调试SPI的过程中遇到一个问题——接收数据整体向左移了一位(1bit)。SPI数据收发是数据交换,因此接收数据时从第二个字节开始才是有效数据,也就是数据整体向右移一个字节(1byte)。请教前辈之后也没有得到解决,通过在网上查阅前人经验终于解决问题,所以写一个避坑经验总结。实际背景:MCU与一款芯片使用spi通信,MCU作为主机,芯片作为从机。这款芯片采用的是它规定的六线SPI,多了两根线:RDY和INT,这样从机就可以主动请求主机给主机发送数据了。一、问题描述根据从机芯片手

最近在学习CAN,记录一下,也供大家参考交流。推荐几个我觉得很好的CAN学习,本文也是在看了他们的好文之后做的笔记首先是瑞萨的CAN入门,真的通透;秀!靠这篇我竟然2天理解了CAN协议!实战STM32F4CAN!原文链接:https://blog.csdn.net/XiaoXiaoPengBo/article/details/116206252CAN详解(小白教程)原文链接:https://blog.csdn.net/xwwwj/article/details/105372234一篇易懂的CAN通讯协议指南1一篇易懂的CAN通讯协议指南1-知乎(zhihu.com)视频推荐CAN总线个人知识总

深度学习部署:Windows安装pycocotools报错解决方法1.pycocotools库的简介2.pycocotools安装的坑3.解决办法更多Ai资讯:公主号AiCharm本系列是作者在跑一些深度学习实例时,遇到的各种各样的问题及解决办法,希望能够帮助到大家。ERROR:Commanderroredoutwithexitstatus1:'D:\Anaconda3\python.exe'-u-c'importsys,setuptools,tokenize;sys.argv[0]='"'"'C:\\Users\\46653\\AppData\\Local\\Temp\\pip-instal