提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

xilinx srio ip学习笔记之初识srio

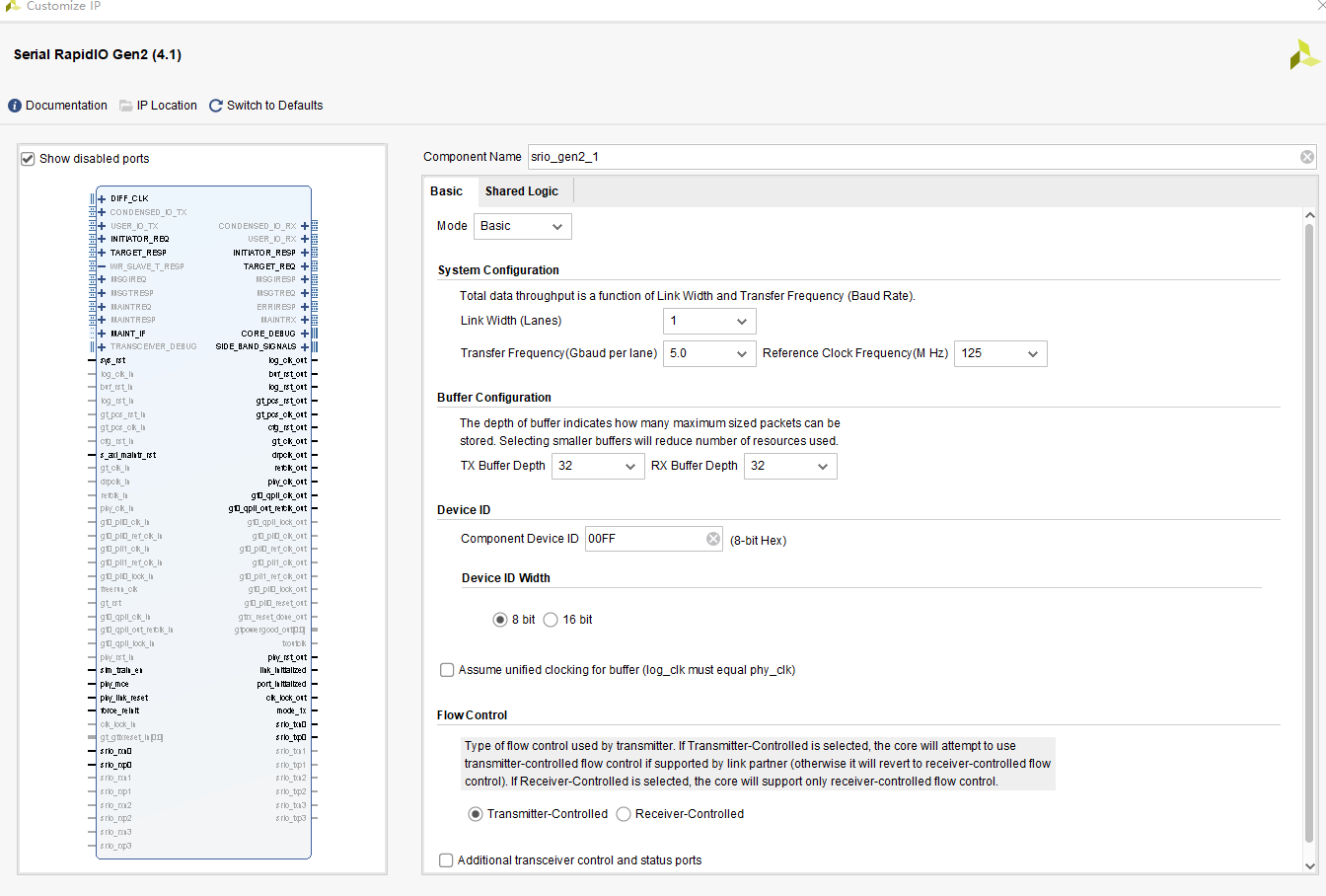

因为工作原因,需要对rapidio 的协议进行了解,在xilinx的IP核中,是对应着Serial RapidIO Gen2 这个IP核。因为之前从来没有接触过这个IP核,因此希望像之前学习JESD IP那样,一开始从xilinx的example开始入手

因为一开始什么都不太明白,所以我一开始对IP的设置保持初始状态,就在这个的基础上生成example

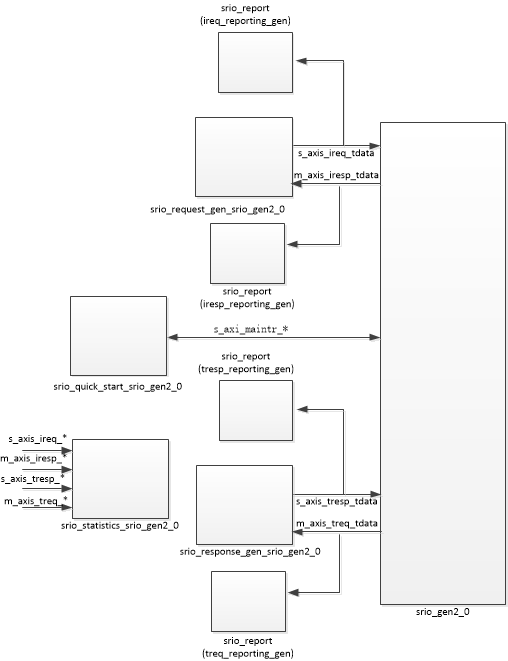

生成example之后,对srio_gen2_0的端口进行简单的观察,发现大部分端口都是输出的,说明大部分端口都不需要进行控制,而里面有几组总线是需要进行控制的

s_axis_ireq_*

m_axis_iresp_*

s_axis_tresp_*

m_axis_treq_*

s_axi_maintr_*

也就是说我们只要关注这些总线如何进行使用。

srio_gen2_0 srio_gen2_0_inst

(//---------------------------------------------------------------

.sys_clkp (sys_clkp ), // input

.sys_clkn (sys_clkn ), // input

.sys_rst (sys_rst ), // input

// all clocks as output in shared logic mode

.log_clk_out (log_clk ), // output

.phy_clk_out (phy_clk ), // output

.gt_clk_out (gt_clk ), // output

.gt_pcs_clk_out (gt_pcs_clk), // output

.drpclk_out (drpclk ), // output

.refclk_out (refclk ), // output

.clk_lock_out (clk_lock ), // output

// all resets as output in shared logic mode

.log_rst_out (log_rst ), // output

.phy_rst_out (phy_rst ), // output

.buf_rst_out (buf_rst ), // output

.cfg_rst_out (cfg_rst ), // output

.gt_pcs_rst_out (gt_pcs_rst), // output

//---------------------------------------------------------------

.gt0_qpll_clk_out (gt0_qpll_clk_out ), // output

.gt0_qpll_out_refclk_out (gt0_qpll_out_refclk_out), // output

// //---------------------------------------------------------------

.srio_rxn0 (srio_rxn0), // input

.srio_rxp0 (srio_rxp0), // input

.srio_txn0 (srio_txn0), // output

.srio_txp0 (srio_txp0), // output

.s_axis_ireq_tvalid (ireq_tvalid), // input

.s_axis_ireq_tready (ireq_tready), // output

.s_axis_ireq_tlast (ireq_tlast), // input

.s_axis_ireq_tdata (ireq_tdata), // input [63 : 0]

.s_axis_ireq_tkeep (ireq_tkeep), // input [7 : 0]

.s_axis_ireq_tuser (ireq_tuser), // input [31 : 0]

.m_axis_iresp_tvalid (iresp_tvalid), // output

.m_axis_iresp_tready (iresp_tready), // input

.m_axis_iresp_tlast (iresp_tlast), // output

.m_axis_iresp_tdata (iresp_tdata), // output [63 : 0]

.m_axis_iresp_tkeep (iresp_tkeep), // output [7 : 0]

.m_axis_iresp_tuser (iresp_tuser), // output [31 : 0]

.s_axis_tresp_tvalid (tresp_tvalid), // input

.s_axis_tresp_tready (tresp_tready), // output

.s_axis_tresp_tlast (tresp_tlast), // input

.s_axis_tresp_tdata (tresp_tdata), // input [63 : 0]

.s_axis_tresp_tkeep (tresp_tkeep), // input [7 : 0]

.s_axis_tresp_tuser (tresp_tuser), // input [31 : 0]

.m_axis_treq_tvalid (treq_tvalid), // output

.m_axis_treq_tready (treq_tready), // input

.m_axis_treq_tlast (treq_tlast), // output

.m_axis_treq_tdata (treq_tdata), // output [63 : 0]

.m_axis_treq_tkeep (treq_tkeep), // output [7 : 0]

.m_axis_treq_tuser (treq_tuser), // output [31 : 0]

.s_axi_maintr_rst (maintr_rst), // input

.s_axi_maintr_awvalid (maintr_awvalid), // input

.s_axi_maintr_awready (maintr_awready), // output

.s_axi_maintr_awaddr (maintr_awaddr), // input [31 : 0]

.s_axi_maintr_wvalid (maintr_wvalid), // input

.s_axi_maintr_wready (maintr_wready), // output

.s_axi_maintr_wdata (maintr_wdata), // input [31 : 0]

.s_axi_maintr_bvalid (maintr_bvalid), // output

.s_axi_maintr_bready (maintr_bready), // input

.s_axi_maintr_bresp (maintr_bresp), // output [1 : 0]

.s_axi_maintr_arvalid (maintr_arvalid), // input

.s_axi_maintr_arready (maintr_arready), // output

.s_axi_maintr_araddr (maintr_araddr), // input [31 : 0]

.s_axi_maintr_rvalid (maintr_rvalid), // output

.s_axi_maintr_rready (maintr_rready), // input

.s_axi_maintr_rdata (maintr_rdata), // output [31 : 0]

.s_axi_maintr_rresp (maintr_rresp), // output [1 : 0]

.sim_train_en (sim_train_en), // input

.phy_mce (phy_mce), // input

.phy_link_reset (phy_link_reset), // input

.force_reinit (force_reinit), // input

.phy_rcvd_mce (phy_rcvd_mce ), // output

.phy_rcvd_link_reset (phy_rcvd_link_reset), // output

.phy_debug (phy_debug ), // output [223 : 0]

.gtrx_disperr_or (gtrx_disperr_or ), // output

.gtrx_notintable_or (gtrx_notintable_or ), // output

.port_error (port_error ), // output

.port_timeout (port_timeout ), // output [23 : 0]

.srio_host (srio_host ), // output

.port_decode_error (port_decode_error ), // output

.deviceid (deviceid ), // output [15 : 0]

.idle2_selected (idle2_selected ), // output

.phy_lcl_master_enable_out (), // these are side band output only signals

.buf_lcl_response_only_out (),

.buf_lcl_tx_flow_control_out (),

.buf_lcl_phy_buf_stat_out (),

.phy_lcl_phy_next_fm_out (),

.phy_lcl_phy_last_ack_out (),

.phy_lcl_phy_rewind_out (),

.phy_lcl_phy_rcvd_buf_stat_out (),

.phy_lcl_maint_only_out (),

//---

//---

.port_initialized (port_initialized ), // output

.link_initialized (link_initialized ), // output

.idle_selected (idle_selected ), // output

.mode_1x (mode_1x ) // output

);

而且通过观察各个总线的tdata的输入输出方向,可以看出

.s_axis_ireq_tvalid (ireq_tvalid), // input

.s_axis_ireq_tready (ireq_tready), // output

.s_axis_ireq_tlast (ireq_tlast), // input

.s_axis_ireq_tdata (ireq_tdata), // input [63 : 0]

.s_axis_ireq_tkeep (ireq_tkeep), // input [7 : 0]

.s_axis_ireq_tuser (ireq_tuser), // input [31 : 0]

上面这组控制线肯定是用于发送数据的

.m_axis_treq_tvalid (treq_tvalid), // output

.m_axis_treq_tready (treq_tready), // input

.m_axis_treq_tlast (treq_tlast), // output

.m_axis_treq_tdata (treq_tdata), // output [63 : 0]

.m_axis_treq_tkeep (treq_tkeep), // output [7 : 0]

.m_axis_treq_tuser (treq_tuser), // output [31 : 0]

而上面这组控制线肯定是用于接收数据的,这两组应该是有对应关系。也就是说从s_axis_ireq_*发送出去的数据应该从m_axis_iresp_*获得。

同样的,

.s_axis_tresp_tvalid (tresp_tvalid), // input

.s_axis_tresp_tready (tresp_tready), // output

.s_axis_tresp_tlast (tresp_tlast), // input

.s_axis_tresp_tdata (tresp_tdata), // input [63 : 0]

.s_axis_tresp_tkeep (tresp_tkeep), // input [7 : 0]

.s_axis_tresp_tuser (tresp_tuser), // input [31 : 0]

上面这组控制线肯定是用于发送数据的

.m_axis_iresp_tvalid (iresp_tvalid), // output

.m_axis_iresp_tready (iresp_tready), // input

.m_axis_iresp_tlast (iresp_tlast), // output

.m_axis_iresp_tdata (iresp_tdata), // output [63 : 0]

.m_axis_iresp_tkeep (iresp_tkeep), // output [7 : 0]

.m_axis_iresp_tuser (iresp_tuser), // output [31 : 0]

而上面这组控制线肯定是用于接收数据的,这两组应该是有对应关系。也就是说从s_axis_tresp_*发送出去的数据应该从m_axis_treq_*获得。

程序框图如下:

以上就是对srio ip example的一个直观的认识,希望后面慢慢能够加深其理解

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

最近在学习CAN,记录一下,也供大家参考交流。推荐几个我觉得很好的CAN学习,本文也是在看了他们的好文之后做的笔记首先是瑞萨的CAN入门,真的通透;秀!靠这篇我竟然2天理解了CAN协议!实战STM32F4CAN!原文链接:https://blog.csdn.net/XiaoXiaoPengBo/article/details/116206252CAN详解(小白教程)原文链接:https://blog.csdn.net/xwwwj/article/details/105372234一篇易懂的CAN通讯协议指南1一篇易懂的CAN通讯协议指南1-知乎(zhihu.com)视频推荐CAN总线个人知识总

深度学习部署:Windows安装pycocotools报错解决方法1.pycocotools库的简介2.pycocotools安装的坑3.解决办法更多Ai资讯:公主号AiCharm本系列是作者在跑一些深度学习实例时,遇到的各种各样的问题及解决办法,希望能够帮助到大家。ERROR:Commanderroredoutwithexitstatus1:'D:\Anaconda3\python.exe'-u-c'importsys,setuptools,tokenize;sys.argv[0]='"'"'C:\\Users\\46653\\AppData\\Local\\Temp\\pip-instal

我完全不是程序员,正在学习使用Ruby和Rails框架进行编程。我目前正在使用Ruby1.8.7和Rails3.0.3,但我想知道我是否应该升级到Ruby1.9,因为我真的没有任何升级的“遗留”成本。缺点是什么?我是否会遇到与普通gem的兼容性问题,或者甚至其他我不太了解甚至无法预料的问题? 最佳答案 你应该升级。不要坚持从1.8.7开始。如果您发现不支持1.9.2的gem,请避免使用它们(因为它们很可能不被维护)。如果您对gem是否兼容1.9.2有任何疑问,您可以在以下位置查看:http://www.railsplugins.or

如何学习ruby的正则表达式?(对于假人) 最佳答案 http://www.rubular.com/在Ruby中使用正则表达式时是一个很棒的工具,因为它可以立即将结果可视化。 关于ruby-我如何学习ruby的正则表达式?,我们在StackOverflow上找到一个类似的问题: https://stackoverflow.com/questions/1881231/

深度学习12.CNN经典网络VGG16一、简介1.VGG来源2.VGG分类3.不同模型的参数数量4.3x3卷积核的好处5.关于学习率调度6.批归一化二、VGG16层分析1.层划分2.参数展开过程图解3.参数传递示例4.VGG16各层参数数量三、代码分析1.VGG16模型定义2.训练3.测试一、简介1.VGG来源VGG(VisualGeometryGroup)是一个视觉几何组在2014年提出的深度卷积神经网络架构。VGG在2014年ImageNet图像分类竞赛亚军,定位竞赛冠军;VGG网络采用连续的小卷积核(3x3)和池化层构建深度神经网络,网络深度可以达到16层或19层,其中VGG16和VGG

文章目录1、自相关函数ACF2、偏自相关函数PACF3、ARIMA(p,d,q)的阶数判断4、代码实现1、引入所需依赖2、数据读取与处理3、一阶差分与绘图4、ACF5、PACF1、自相关函数ACF自相关函数反映了同一序列在不同时序的取值之间的相关性。公式:ACF(k)=ρk=Cov(yt,yt−k)Var(yt)ACF(k)=\rho_{k}=\frac{Cov(y_{t},y_{t-k})}{Var(y_{t})}ACF(k)=ρk=Var(yt)Cov(yt,yt−k)其中分子用于求协方差矩阵,分母用于计算样本方差。求出的ACF值为[-1,1]。但对于一个平稳的AR模型,求出其滞

前面一篇关于智能合约翻译文讲到了,是一种计算机程序,既然是程序,那就可以使用程序语言去编写智能合约了。而若想玩区块链上的项目,大部分区块链项目都是开源的,能看得懂智能合约代码,或找出其中的漏洞,那么,学习Solidity这门高级的智能合约语言是有必要的,当然,这都得在公链``````以太坊上,毕竟国内的联盟链有些是不兼容Solidity。Solidity是一种面向对象的高级语言,用于实现智能合约。智能合约是管理以太坊状态下的账户行为的程序。Solidity是运行在以太坊(Ethereum)虚拟机(EVM)上,其语法受到了c++、python、javascript影响。Solidity是静态类型

写在之前Shader变体、Shader属性定义技巧、自定义材质面板,这三个知识点任何一个单拿出来都是一套知识体系,不能一概而论,本文章目的在于将学习和实际工作中遇见的问题进行总结,类似于网络笔记之用,方便后续回顾查看,如有以偏概全、不祥不尽之处,还望海涵。1、Shader变体先看一段代码......Properties{ [KeywordEnum(on,off)]USL_USE_COL("IsUseColorMixTex?",int)=0 [Toggle(IS_RED_ON)]_IsRed("IsRed?",int)=0}......//中间省略,后续会有完整代码 #pragmamulti_c

TCL脚本语言简介•TCL(ToolCommandLanguage)是一种解释执行的脚本语言(ScriptingLanguage),它提供了通用的编程能力:支持变量、过程和控制结构;同时TCL还拥有一个功能强大的固有的核心命令集。TCL经常被用于快速原型开发,脚本编程,GUI和测试等方面。•实际上包含了两个部分:一个语言和一个库。首先,Tcl是一种简单的脚本语言,主要使用于发布命令给一些互交程序如文本编辑器、调试器和shell。由于TCL的解释器是用C\C++语言的过程库实现的,因此在某种意义上我们又可以把TCL看作C库,这个库中有丰富的用于扩展TCL命令的C\C++过程和函数,所以,Tcl是