三八译码器,即是 3 种输入状态翻译成 8 种输出状态。

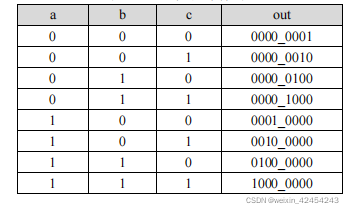

真值表

代码展示

module decoder_3_8(a,b,c,out);

input a;//输入端口a

input b;//输入端口b

input c;//输入端口c

output [7:0] out;//输出端口out

reg [7:0] out;

//或者用output reg [7:0] out

//以always块描述的信号赋值,被赋值的对象必须要定义成reg类型

always@(a,b,c)begin //相当于always@(*),*就代指以上所有输入变量

case({a,b,c})//位拼接,{a,b,c}变成了一个三位的信号

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;//3'd5 :out = 8'b0010_0000

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

/*

3'd0:out = 8'b0000_0001;//下划线 _ 是为了增强代码的可读性。

3'd1:out = 8'b0000_0010;

3'd2:out = 8'b0000_0100;

3'd3:out = 8'b0000_1000;

3'd4:out = 8'b0001_0000;

3'd5:out = 8'b0010_0000;

3'd6:out = 8'b0100_0000;

3'd7:out = 8'b1000_0000; //注意这里的跨行注释方法 /*和*/

*/

endcase

end

endmodule

testbench

`timescale 1ns/1ns

module decoder_3_8_tb();

reg s_a;

reg s_b;

reg s_c;

wire [7:0] out;

decoder_3_8 decoder_3_8(

.a(s_a),

.b(s_b),

.c(s_c),

.out(out)

);

initial begin

s_a=0;s_b=0;s_c=0; //在0时刻三个输入均为0

#200; //经过200ns的延时

s_a=0;s_b=0;s_c=1; //在200ns时输入信号的值

#200; //又经过200ns的延时

s_a=0;s_b=1;s_c=0; //在400ns时输入信号的值

#200; //又经过200ns的延时

s_a=0;s_b=1;s_c=1; //在600ns时输入信号的值

#200;

s_a=1;s_b=0;s_c=0;

#200;

s_a=1;s_b=0;s_c=1;

#200;

s_a=1;s_b=1;s_c=0;

#200;

s_a=1;s_b=1;s_c=1;

#200;

$stop; //停止仿真

end

endmodule

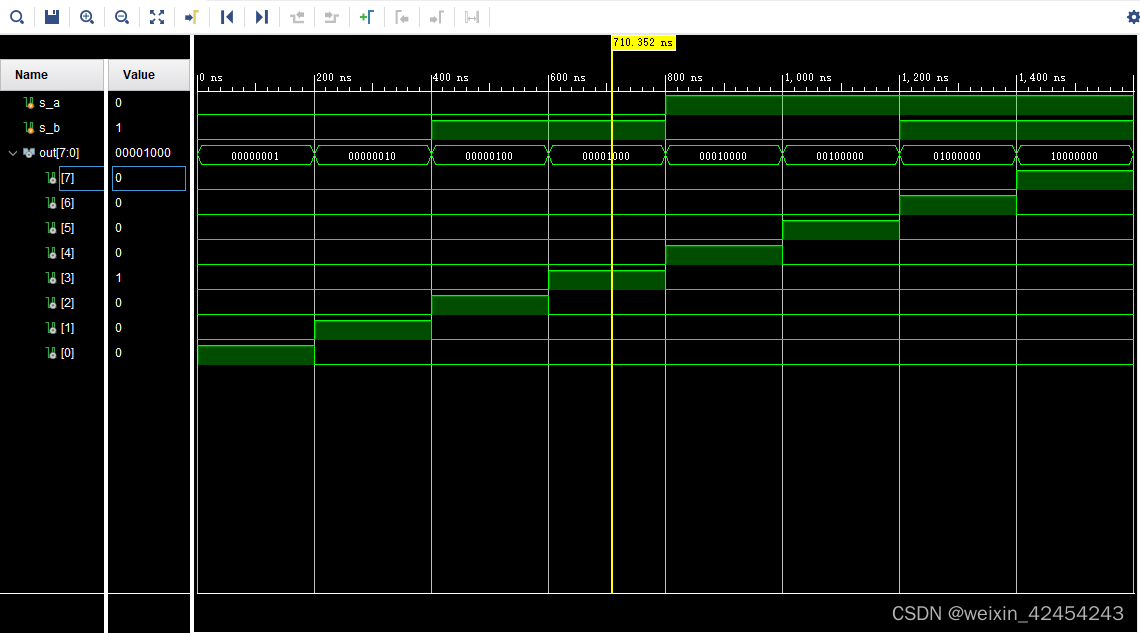

仿真图

补充

(1)always语句两种触发方式

a、第一种是电平触发,例如always @(a or b or c),a、b、c均为变量,当其中一个发生变化时,下方的语句将被执行。

b、第二种是沿触发,例如always @(posedge clk or negedge rstn),即当时钟处在上升沿或下降沿时,语句被执行。

c、而对于always@(),意思是以上两种触发方式都包含在内,任意一种发生变化都会触发该语句。

(2)数字声明

数字声明时,合法的基数格式有 4 种,包括:十进制('d 或 'D),十六进制('h 或 'H),二进制('b 或 'B),八进制('o 或 'O)。

数字10的不同表示方式,'前面的数字表示位数,'后面的一个字母字母表示进制格式

b 二进制 4'b1010

0 八进制 2'o12

d 十进制 2'd10

h 十六进制 1'ha(3)数值的种类

wire 和reg这两种数据类型的变量在定义时要设置位宽,缺省为1位。变量的每一位可以是0,1,X,Z。其中x代表一个未被预置初始状态的变量或者是由于由两个或多个驱动装置试图将之设定为不同的值而引起的冲突型线型变量。z代表高阻状态或浮空量

Verilog HDL 有下列四种基本的值来表示硬件电路中的电平逻辑:

0:逻辑 0 或 "假"

1:逻辑 1 或 "真"

x 或 X:未知

z 或 Z:高阻

x 意味着信号数值的不确定,即在实际电路里,信号可能为 1,也可能为 0。

z 意味着信号处于高阻状态,常见于信号(input, reg)没有驱动时的逻辑结果。例如一个 pad 的 input 呈现高阻状态时,其逻辑值和上下拉的状态有关系。上拉则逻辑值为 1,下拉则为 0 。

(4)数据的类型

Verilog 最常用的 2 种数据类型就是线型(wire)与寄存器型(reg),其余类型可以理解为这两种数据类型的扩展或辅助。

a、线网(wire)使用在连续赋值语句中

相当于一根电线,用来连接电路,不能存储数据,无驱动能力,只能在assign左侧赋值。

wire型数据常用来表示以assign关键字指定的组合逻辑信号。模块的输入输出端口类型都默认为wire型(默认初始值是z)不指定就默认为1位wire类型,专门指定出wire类型,可能是多位或为使程序易读。

wire表示直通,即只要输入有变化,输出马上无条件地反映。

线网型还有其他数据类型,包括 wand,wor,wri,triand,trior,trireg 等。这些数据类型用的频率不是很高。

b、寄存器(reg)使用在过程赋值语句中

always模块内被赋值的信号,必须定义为reg型,默认初始值是x。

reg表示一定要有触发,输出才会反映输入。

reg只能在initial和always中赋值。

reg可以综合成register,latch,甚至wire(当其只是中间变量的时候),可以用于组合逻辑或者时序逻辑,能存储数据,有驱动能力,在always @模块表达式左侧被赋值。

寄存器(reg)用来表示存储单元,它会保持数据原有的值,直到被改写。

c、两者的共同点

都能用于assign与always @模块表达式的右侧。

d、连续赋值语句和过程赋值语句

在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧。在理解上,相当于一个逻辑之后直接连了一条线,这个逻辑对应于表达式的右侧,而这条线就对应于wire。

在过程赋值语句中,表达式右侧的计算结果在某种条件的触发下放到一个变量当中,而这个变量可以声明成reg类型的。根据触发条件的不同,过程赋值语句可以建模不同的硬件结构:如果这个条件是时钟的上升沿或下降沿,那么这个硬件模型就是一个触发器;如果这个条件是某一信号的高电平或低电平,那么这个硬件模型就是一个锁存器;如果这个条件是赋值语句右侧任意操作数的变化,那么这个硬件模型就是一个组合逻辑。

e、综合之后的区别

wire型的变量综合出来一般是一根导线;

reg变量在always块中有两种情况: always后的敏感表中是(a or b or c)形式的,也就是不带时钟边沿的,综合出来还是组合逻辑 always后的敏感表中是(posedge clk)形式的,也就是带边沿的,综合出来一般是时序逻辑,会包含触发器(Flip-Flop)

在设计中,输入信号一般来说你是不知道上一级是寄存器输出还是组合逻辑输出,那么对于本级来说就是一根导线,也就是wire型。而输出信号则由你自己来决定是寄存器输出还是组合逻辑输出,wire型、reg型都可以。但一般的,整个设计的外部输出(即最顶层模块的输出),要求是寄存器输出,较稳定、扇出能力也较好。

(5)

输入端口可以由net/reg驱动,但输入端口只能是net,如a = b & c,输入端口a 只能是net型,但其驱动b,c可以是net/reg型;

输出端口可以使net/reg类型,输出端口只能驱动net,如a = b & c,模块的输出端口b,c可以是net/reg型,但它们驱动的a必须是net型;若输出端口在过程块(always/initial)中赋值则为reg型,若在过程块外赋值则为net型。用关键词inout声明一个双向端口, inout端口不能声明为寄存器类型,只能是net类型。

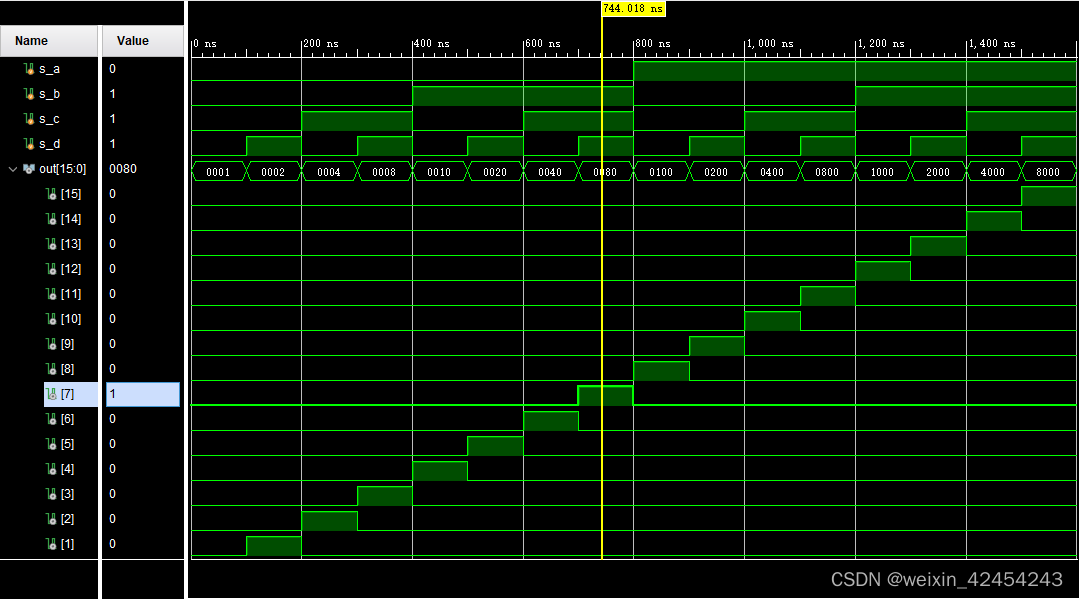

(6)课后作业

实现4-16译码器

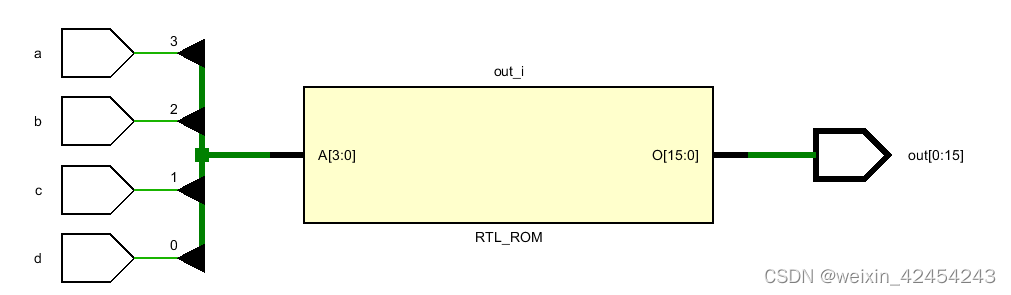

a、原理框图

`timescale 1ns / 1ns

module decoder_4_16(a,b,c,d,out

);

input a;

input b;

input c;

input d;

output reg[15:0] out;

always@(a,b,c,d)begin

case({a,b,c,d})

4'b0000:out=16'b0000_0000_0000_0001;

4'b0001:out=16'b0000_0000_0000_0010;

4'b0010:out=16'b0000_0000_0000_0100;

4'b0011:out=16'b0000_0000_0000_1000;

4'b0100:out=16'b0000_0000_0001_0000;

4'b0101:out=16'b0000_0000_0010_0000;

4'b0110:out=16'b0000_0000_0100_0000;

4'b0111:out=16'b0000_0000_1000_0000;

4'b1000:out=16'b0000_0001_0000_0000;

4'b1001:out=16'b0000_0010_0000_0000;

4'b1010:out=16'b0000_0100_0000_0000;

4'b1011:out=16'b0000_1000_0000_0000;

4'b1100:out=16'b0001_0000_0000_0000;

4'b1101:out=16'b0010_0000_0000_0000;

4'b1110:out=16'b0100_0000_0000_0000;

4'b1111:out=16'b1000_0000_0000_0000;

/* 2'd00:out=16'b0000_0000_0000_0001;

2'd01:out=16'b0000_0000_0000_0010;

2'd02:out=16'b0000_0000_0000_0100;

2'd03:out=16'b0000_0000_0000_1000;

2'd04:out=16'b0000_0000_0001_0000;

2'd05:out=16'b0000_0000_0010_0000;

2'd06:out=16'b0000_0000_0100_0000;

2'd07:out=16'b0000_0000_1000_0000;

2'd08:out=16'b0000_0001_0000_0000;

2'd09:out=16'b0000_0010_0000_0000;

2'd10:out=16'b0000_0100_0000_0000;

2'd11:out=16'b0000_1000_0000_0000;

2'd12:out=16'b0001_0000_0000_0000;

2'd13:out=16'b0010_0000_0000_0000;

2'd14:out=16'b0100_0000_0000_0000;

2'd15:out=16'b1000_0000_0000_0000;*/

endcase

end

endmodule

`timescale 1ns / 1ns

module decoder_4_16_tb(

);

reg s_a;

reg s_b;

reg s_c;

reg s_d;

wire [15:0] out;

decoder_4_16 decoder_4_16(

.a(s_a),

.b(s_b),

.c(s_c),

.d(s_d),

.out(out)

);

initial begin

s_a=0;s_b=0;s_c=0;s_d=0;

#100;

s_a=0;s_b=0;s_c=0;s_d=1;

#100;

s_a=0;s_b=0;s_c=1;s_d=0;

#100;

s_a=0;s_b=0;s_c=1;s_d=1;

#100;

s_a=0;s_b=1;s_c=0;s_d=0;

#100;

s_a=0;s_b=1;s_c=0;s_d=1;

#100;

s_a=0;s_b=1;s_c=1;s_d=0;

#100;

s_a=0;s_b=1;s_c=1;s_d=1;

#100;

s_a=1;s_b=0;s_c=0;s_d=0;

#100;

s_a=1;s_b=0;s_c=0;s_d=1;

#100;

s_a=1;s_b=0;s_c=1;s_d=0;

#100;

s_a=1;s_b=0;s_c=1;s_d=1;

#100;

s_a=1;s_b=1;s_c=0;s_d=0;

#100;

s_a=1;s_b=1;s_c=0;s_d=1;

#100;

s_a=1;s_b=1;s_c=1;s_d=0;

#100;

s_a=1;s_b=1;s_c=1;s_d=1;

#100;

end

endmodule

目录前言一、定时器部分和按键部分二、PWM调速三、电机驱动部分三、编码器接口部分(测速)四.主函数总结推荐STM32学习课程:[6-8]编码器接口测速_哔哩哔哩_bilibili[6-8]编码器接口测速是STM32入门教程-2022持续更新中的第20集视频,该合集共计30集,视频收藏或关注UP主,及时了解更多相关视频内容。https://www.bilibili.com/video/BV1th411z7sn/?p=20&spm_id_from=pageDriver&vd_source=ed36b2700bbc2bac7746c270bc391540OLED显示屏代码

计数器同样由三个模块构成,分别为:顶层,计数器和译码器。一、实验任务大家这会儿数电理论课应该还没学到这里,所以对以上的部分名词进行解释:1.异步清零(clr)指不管现在时钟信号(clk)是什么,跑到哪儿了,只要你按下异步清零的按钮,计数器就应该马上归零。2.同步使能(en)其实就是一个计数器是否开始工作的开关,关闭了使能开关,计数器将会停在当前的计数值,不再随时间信号进行计数。3.同步置数(load)一个非常面向使用对象的功能。让使用者输入一个数值(预置数),再从这个数值进行加/减计数,因为是随着下一个时钟信号的到来才开始计数的,所以叫同步置数。二、实验分析输入信号:clkin(时钟),clr

我正在使用带有选项的谷歌地理编码器仅返回来自德国的结果这是我函数的相关部分...vargeocoder=newgoogle.maps.Geocoder();geocoder.geocode({"address":address,"region":"DE"},function(results,status){if(status==google.maps.GeocoderStatus.OK){if(results[0].geometry.location){completeGeo(results[0],address);}else{completeGeo(null,address);}..

优先编码器(PriorityEncoder,PENC)用于判断数据最高位1出现的位置。以4-2优先编码器(PENC)为例,其真值表为:D3D2D1D0Q1Q2Vld0001001001x01101xx1011xxx1110000xx0用卡诺图表示为 Q0=D3+(~D2)D1 Q1=D3+D2Vld=D3+D2+D1+D0优先编码器是可扩展的,获得8-3PENC只需要对两级4-2PENC的输出进行处理即可。8-3PENC真值表可简化为:可以获知:Q[1:0]为PENC_L或PENC_H的输出,

我们有一个数组,每个页面上都有许多属性。有时它有一个“值”属性。我们使用myArrayObject['values']检查它并期望是字符串或未定义。更新到Chrome38后myArrayObject['values']返回functionvalues(){[nativecode]}经过一番挖掘,这似乎与V8ticket有关实现@@unscopablesforthe6thEditionofecmascript.这些变化是committed两个月前。不久后,一名开发人员试图rollthembackwiththenotethattheywere"web-breaking".所以问题是,Arr

geo=function(options){geocoder.geocode(options,function(results,status){if(status==google.maps.GeocoderStatus.OK){varx=results;alert('pear');returnx;}else{return-1;}});}getAddr=function(addr){if(typeofaddr!='undefined'&&addr!=null){varblah=geo({address:addr,});alert('apple');returnblah;}return-1

自监督学习之掩码自动编码器(MaskedAutoencoders,MAE)——音频识别方面1.参考文献《MaskedAutoencodersthatListen》2.背景Transformers和self-supervisedlearning(自监督学习)占据了计算机视觉(ComputerVision,CV)和自然语言处理(naturallanguageprocessing,NLP)的主导地位。使用BERT进行屏蔽自动编码,通过对大规模语言语料库的自监督预训练,为各种NLP任务提供了一种新的最新技术。类似地,在CV社区中,VisionTransformers(ViT)变得越来越流行,在自监督的

我浏览了几个网站,但没有找到用javascript解码QR码图像的代码片段。我浏览了qrCode.js但它只有QRcodegenerator。我正在寻找可以解码base64二维码图像并获取详细信息的二维码解码器。 最佳答案 有一个用于读取二维码的Java库的JavaScript端口:WebQR代码可以在GitHub上找到自述文件:Usage:Includethescriptsinthefollowingorder:Togetthedecodedinformationset:qrcode.callback=function(decod

我想了解gob是如何工作的。我有几个问题。我知道gob序列化了一个像structmap或interface这样的go类型(我们必须注册它的真实类型)但是:func(dec*Decoder)Decode(einterface{})errorDecodereadsthenextvaluefromtheinputstreamandstoresitinthedatarepresentedbytheemptyinterfacevalue.Ifeisnil,thevaluewillbediscarded.Otherwise,thevalueunderlyingemustbeapointertoth

如何将*string转换为string?这是我的错误代码:cannotusem.Body(type*string)astypestringinargumenttostrings.NewReader这是我的代码:dec:=json.NewDecoder(strings.NewReader(m.Body)) 最佳答案 取消引用指针以从*string获取string的值,然后在strings.NewReader函数中使用它。例如:-strValue:=*m.Bodydec:=json.NewDecoder(strings.NewReade