Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

毫不夸张的说,对于稍微复杂的 Verilog 设计,如果不进行仿真,即便是经验丰富的老手,99.9999% 以上的设计都不会正常的工作。不能说仿真比设计更加的重要,但是一般来说,仿真花费的时间会比设计花费的时间要多。有时候,考虑到各种应用场景,testbench 的编写也会比 Verilog 设计更加的复杂。所以,数字电路行业会具体划分设计工程师和验证工程师。

下面,对 testbench 做一个简单的学习。

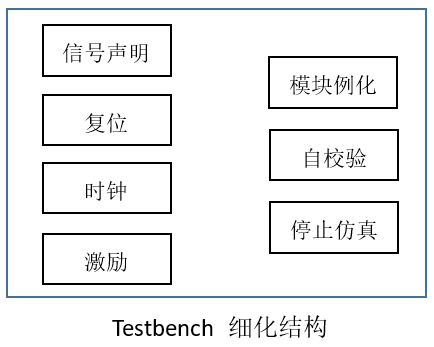

其实 testbench 最基本的结构包括信号声明、激励和模块例化。

根据设计的复杂度,需要引入时钟和复位部分。当然更为复杂的设计,激励部分也会更加复杂。根据自己的验证需求,选择是否需要自校验和停止仿真部分。

当然,复位和时钟产生部分,也可以看做激励,所以它们都可以在一个语句块中实现。也可以拿自校验的结果,作为结束仿真的条件。

实际仿真时,可以根据自己的个人习惯来编写 testbench,这里只是做一份个人的总结。

前面的章节中,已经写过很多的 testbench。其实它们的结构也都大致相同。

下面,我们举一个数据拼接的简单例子,对 testbench 再做一个具体的分析。

一个 2bit 数据拼接成 8bit 数据的功能模块描述如下:

module data_consolidation

(

input clk ,

input rstn ,

input [1:0] din , //data in

input din_en ,

output [7:0] dout ,

output dout_en //data out

);

// data shift and counter

reg [7:0] data_r ;

reg [1:0] state_cnt ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

state_cnt <= 'b0 ;

data_r <= 'b0 ;

end

else if (din_en) begin

state_cnt <= state_cnt + 1'b1 ; //数据计数

data_r <= {data_r[5:0], din} ; //数据拼接

end

else begin

state_cnt <= 'b0 ;

end

end

assign dout = data_r ;

// data output en

reg dout_en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

dout_en_r <= 'b0 ;

end

//计数为 3 且第 4 个数据输入时,同步输出数据输出使能信号

else if (state_cnt == 2'd3 & din_en) begin

dout_en_r <= 1'b1 ;

end

else begin

dout_en_r <= 1'b0 ;

end

end

//这里不直接声明dout_en为reg变量,而是用相关寄存器对其进行assign赋值

assign dout_en = dout_en_r;

endmodule

对应的 testbench 描述如下,增加了文件读写的语句:

`timescale 1ns/1ps

//============== (1) ==================

//signals declaration

module test ;

reg clk;

reg rstn ;

reg [1:0] din ;

reg din_en ;

wire [7:0] dout ;

wire dout_en ;

//============== (2) ==================

//clock generating

real CYCLE_200MHz = 5 ; //

always begin

clk = 0 ; #(CYCLE_200MHz/2) ;

clk = 1 ; #(CYCLE_200MHz/2) ;

end

//============== (3) ==================

//reset generating

initial begin

rstn = 1'b0 ;

#8 rstn = 1'b1 ;

end

//============== (4) ==================

//motivation

int fd_rd ;

reg [7:0] data_in_temp ; //for self check

reg [15:0] read_temp ; //8bit ascii data, 8bit \n

initial begin

din_en = 1'b0 ; //(4.1)

din = 'b0 ;

open_file("../tb/data_in.dat", "r", fd_rd); //(4.2)

wait (rstn) ; //(4.3)

# CYCLE_200MHz ;

//read data from file

while (! $feof(fd_rd) ) begin //(4.4)

@(negedge clk) ;

$fread(read_temp, fd_rd);

din = read_temp[9:8] ;

data_in_temp = {data_in_temp[5:0], din} ;

din_en = 1'b1 ;

end

//stop data

@(posedge clk) ; //(4.5)

#2 din_en = 1'b0 ;

end

//open task

task open_file;

input string file_dir_name ;

input string rw ;

output int fd ;

fd = $fopen(file_dir_name, rw);

if (! fd) begin

$display("--- iii --- Failed to open file: %s", file_dir_name);

end

else begin

$display("--- iii --- %s has been opened successfully.", file_dir_name);

end

endtask

//============== (5) ==================

//module instantiation

data_consolidation u_data_process

(

.clk (clk),

.rstn (rstn),

.din (din),

.din_en (din_en),

.dout (dout),

.dout_en (dout_en)

);

//============== (6) ==================

//auto check

reg [7:0] err_cnt ;

int fd_wr ;

initial begin

err_cnt = 'b0 ;

open_file("../tb/data_out.dat", "w", fd_wr);

forever begin

@(negedge clk) ;

if (dout_en) begin

$fdisplay(fd_wr, "%h", dout);

end

end

end

always @(posedge clk) begin

#1 ;

if (dout_en) begin

if (data_in_temp != dout) begin

err_cnt = err_cnt + 1'b1 ;

end

end

end

//============== (7) ==================

//simulation finish

always begin

#100;

if ($time >= 10000) begin

if (!err_cnt) begin

$display("-------------------------------------");

$display("Data process is OK!!!");

$display("-------------------------------------");

end

else begin

$display("-------------------------------------");

$display("Error occurs in data process!!!");

$display("-------------------------------------");

end

#1 ;

$finish ;

end

end

endmodule // test

仿真结果如下。由图可知,数据整合功能的设计符合要求:

1)信号声明

testbench 模块声明时,一般不需要声明端口。因为激励信号一般都在 testbench 模块内部,没有外部信号。

声明的变量应该能全部对应被测试模块的端口。当然,变量不一定要与被测试模块端口名字一样。但是被测试模块输入端对应的变量应该声明为 reg 型,如 clk,rstn 等,输出端对应的变量应该声明为 wire 型,如 dout,dout_en。

2)时钟生成

生成时钟的方式有很多种,例如以下两种生成方式也可以借鉴。

initial clk = 0 ;

always #(CYCLE_200MHz/2) clk = ~clk;

initial begin

clk = 0 ;

forever begin

#(CYCLE_200MHz/2) clk = ~clk;

end

end

需要注意的是,利用取反方法产生时钟时,一定要给 clk 寄存器赋初值。

利用参数的方法去指定时间延迟时,如果延时参数为浮点数,该参数不要声明为 parameter 类型。例如实例中变量 CYCLE_200MHz 的值为 2.5。如果其变量类型为 parameter,最后生成的时钟周期很可能就是 4ns。当然,timescale 的精度也需要提高,单位和精度不能一样,否则小数部分的时间延迟赋值也将不起作用。

3)复位生成

复位逻辑比较简单,一般赋初值为 0,再经过一段小延迟后,复位为 1 即可。

这里大多数的仿真都是用的低有效复位。

4)激励部分

激励部分该产生怎样的输入信号,是根据被测模块的需要来设计的。

本次实例中:

利用系统任务 $fread ,通过句柄信号 fd_rd 将读取的 16bit 数据变量送入到 read_temp 缓存。

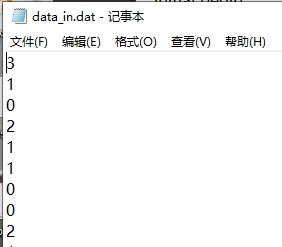

输入数据文件前几个数据截图如下。因为 $fread 只能读取 2 进制文件,所以输入文件的第一行对应的 ASCII 码应该是 330a,所以我们想要得到文件里的数据 3,应该取变量 read_temp 的第 9 到第 8bit 位的数据。

信号 data_in_temp 是对输入数据信号的一个紧随的整合,后面校验模块会以此为参考,来判断仿真是否正常,模块设计是否正确。

当数据量相对较少时,可以利用 Verilog 中的系统任务 $readmemh 来按行直接读取 16 进制数据。保持文件 data_in.dat 内数据和格式不变,则该激励部分可以描述为:

reg [1:0] data_mem [39:0] ;

reg [7:0] data_in_temp ; //for self check

integer k1 ;

initial begin

din_en = 1'b0 ;

din = 'b0 ;

$readmemh("../tb/data_in.dat", data_mem);

wait (rstn) ;

# CYCLE_200MHz ;

//read data from file

for(k1=0; k1<40; k1=k1+1) begin

@(negedge clk) ;

din = data_mem[k1] ;

data_in_temp = {data_in_temp[5:0], din} ;

din_en = 1'b1 ;

end

//stop data

@(posedge clk) ;

#2 din_en = 1'b0 ;

end

5)模块例化

这里利用 testbench 开始声明的信号变量,对被测试模块进行例化连接。

6)自校验

如果设计比较简单,完全可以通过输入、输出信号的波形来确定设计是否正确,此部分完全可以删除。如果数据很多,有时候拿肉眼观察并不能对设计的正确性进行一个有效判定。此时加入一个自校验模块,会大大增加仿真的效率。

实例中,我们会在数据输出使能 dout_en 有效时,对输出数据 dout 与参考数据 read_temp(激励部分产生)做一个对比,并将对比结果置于信号 err_cnt 中。最后就可以通过观察 err_cnt 信号是否为 0 来直观的对设计的正确性进行判断。

当然如实例中所示,我们也可以将数据写入到对应文件中,利用其他方式做对比。

7)结束仿真

如果我们不加入结束仿真部分,仿真就会无限制的运行下去,波形太长有时候并不方便分析。Verilog 中提供了系统任务 $finish 来停止仿真。

停止仿真之前,可以将自校验的结果,通过系统任务 $display 在终端进行显示。

用于打开文件的系统任务 $fopen 格式如下:

fd = $fopen("<name_of_file>", "mode")

和 C 语言类似,打开方式的选项 "mode" 意义如下:

| r | 只读打开一个文本文件,只允许读数据。 |

|---|---|

| w | 只写打开一个文本文件,只允许写数据。如果文件存在,则原文件内容会被删除。如果文件不存在,则创建新文件。 |

| a | 追加打开一个文本文件,并在文件末尾写数据。如果文件如果文件不存在,则创建新文件。 |

| rb | 只读打开一个二进制文件,只允许读数据。 |

| wb | 只写打开或建立一个二进制文件,只允许写数据。 |

| ab | 追加打开一个二进制文件,并在文件末尾写数据。 |

| r+ | 读写打开一个文本文件,允许读和写 |

| w+ | 读写打开或建立一个文本文件,允许读写。如果文件存在,则原文件内容会被删除。如果文件不存在,则创建新文件。 |

| a+ | 读写打开一个文本文件,允许读和写。如果文件不存在,则创建新文件。读取文件会从文件起始地址的开始,写入只能是追加模式。 |

| rb+ | 读写打开一个二进制文本文件,功能与 "r+" 类似。 |

| wb+ | 读写打开或建立一个二进制文本文件,功能与 "w+" 类似。 |

| ab+ | 读写打开一个二进制文本文件,功能与 "a+" 类似。 |

目录0专栏介绍1平面2R机器人概述2运动学建模2.1正运动学模型2.2逆运动学模型2.3机器人运动学仿真3动力学建模3.1计算动能3.2势能计算与动力学方程3.3动力学仿真0专栏介绍?附C++/Python/Matlab全套代码?课程设计、毕业设计、创新竞赛必备!详细介绍全局规划(图搜索、采样法、智能算法等);局部规划(DWA、APF等);曲线优化(贝塞尔曲线、B样条曲线等)。?详情:图解自动驾驶中的运动规划(MotionPlanning),附几十种规划算法1平面2R机器人概述如图1所示为本文的研究本体——平面2R机器人。对参数进行如下定义:机器人广义坐标

目录一、inout在设计文件中的使用方法1.1、inout的第一种使用方法1.2、inout实现的第二种使用方法1.3、inout使用总结 二、inout在仿真测试中的使用方法一、inout在设计文件中的使用方法在FPGA的设计过程中,有时候会遇到双向信号(既能作为输出,也能作为输入的信号叫双向信号)。比如,IIC总线中的SDA信号就是一个双向信号,QSPIFlash的四线操作的时候四根信号线均为双向信号。在Verilog中用关键字inout定义双向信号,这里总结一下双向信号的处理方法。1.1、inout的第一种使用方法 实际上,双向信号的本质是由一个三态门组成的,三态门可以输出高电平,低电

一、机器人介绍 此处是基于MATLABRVC工具箱,对ABB-IRB-1200型号的微型机械臂进行正逆向运动学分析,并利Simulink工具实现对机械臂进行具有动力学参数的末端轨迹规划仿真,最后根据机械模型设计Simulink-Adams联合仿真。 图1.ABBIRB 1200尺寸参数示意图ABBIRB 1200提供的两种型号广泛适用于各作业,且两者间零部件通用,两种型号的工作范围分别为700 mm 和 900 mm,大有效负载分别为 7 kg 和5 kg。 IRB 1200 能够在狭小空间内能发挥其工作范围与性能优势,具有全新的设计、小型化的体积、高效的性能、易于集成、便捷的接

1、单片机控制液晶显示模块1602LCD的显示。液晶显示器(LiquidCrystalDisplay,LCD)具有省电、体积小、抗干扰能力强等优点,LCD显示器分为字段型、字符型和点阵图形型。(1)字段型。以长条状组成字符显示,主要用于数字显示,也可用于显示西文字母或某些字符,广泛用于电子表、计算器、数字仪表中。(2)字符型。专门用于显示字母、数字、符号等。一个字符由5、7或5、10的点阵组成,在单片机系统中已广泛使用(3)点阵图形型。广泛用于图形显示,如笔记本电脑、彩色电视和游戏机等。它是在平板上排列的多行列的矩阵式的晶格点,点大小与多少决定了显示的清晰度。引脚包括8条数据线、3条控制线和3

⏩大家好哇!我是小光,嵌入式爱好者,一个想要成为系统架构师的大三学生。⏩去年下半年参加了全国仿真创新大赛,也是取得了国赛三等奖,省赛一等奖的好成绩。⏩本篇文章对我们的参赛作品《智能鱼缸》做一个简介。⏩感谢你的阅读,不对的地方欢迎指正。⏩如果对代码和文档有需要私信我。————————————————智能鱼缸一、需求分析二、技术方案三、功能展示proteus仿真展示实物展示四、应用前景五、总结一、需求分析随着我国经济的发展和人民生活水平的日益增长,人们的消费观在改变,消费档次与生平都在提高,人们的生活品位越来越高,环境的个性化、环保化越来越受到人们的重视,与之相关的休闲、居家装饰等行业相应的日线蓬

是否有可能以某种方式在Javascript中模拟单精度float?根据DougCrockford的博客“Numberis64-bitfloatingpoint”,但我必须使用单个来移植计算单精度float误差的C++算法。 最佳答案 ES6标准有Math.fround()将float64转换为float32然后再返回,有效地将float舍入为float32精度。参见thisarticle了解详情。 关于javascript-Javascript中的单精度float仿真(float32),

工欲善其事,必先利其器。应该没有多少人会使用Quartus和vivado这些软件自带的编辑器吧,原因在于这些编辑器效率很低,VerilogHDL代码格式比较固定,通常可以利用代码片段补全加快书写。基本上代码写完之后才会打开Quartus或者vivado建立工程,这其实要求编辑器需要有代码检错的功能,否则可能编译时一直报错,什么信号没定义,信号定义错误之类的。Vscode利用插件可以实现此功能,可以达到一次设计就通过编译和仿真。1、vscode安装及解决下载速度慢 首先通过VisualStudioCode-CodeEditing.Redefined安装vscode软件,如图1下载64位vs

推荐阅读CSDN主页GitHub开源地址Unity3D插件分享简书地址我的个人博客大家好,我是佛系工程师☆恬静的小魔龙☆,不定时更新Unity开发技巧,觉得有用记得一键三连哦。一、前言在日常虚拟仿真项目开发中,可能会遇到要输入表格数据的情况,表格通常是使用UI的InputField组件生成,在输入数据的时候,需要输入→点击下一个输入框→再输入的流程,比较麻烦。因此,写了一个小工具,将这个脚本附到所有组成表格的InputField的父节点上,就可以实现Tab或者Enter实现换行,也就是切换到下一个输入框的功能。效果图:二、实现效果新建脚本TabInputField.cs,双击打开脚本编辑代码:

普遍的网络共识似乎是,如果您在chrome模拟器中看到一个名称,您可以在Protractor配置中按原样使用它...所以我尝试了AppleiPad:{browserName:'chrome',chromeOptions:{mobileEmulation:{deviceName:'AppleiPad'}}}但我不得不四处乱逛,直到反复试验得出正确的设备名称为:AppleiPad3/4现在我在这里搜索:https://developer.chrome.com/devtools/docs/device-mode#enable-device-mode在这里:https://sites.goog

前言:验证结构与实验3是相同的,但需要验证的对象是完整的mcdf。对比之前新添加了reg寄存器模块(选择数据),formatter模块(数据打包)。种一棵树最好的时间是十年前,其次是现在。不是吗?实验3结构包含moinitor、checker、generator、initiator、test,这已经是一个完整的仿真结构,实验4可以说是实验3结构的复制粘贴。实验4将设计变得更复杂,添加了reg寄存器模块,formatter模块。验证过程完全相同,需要像实验3的验证过程一样对这两个模块也做仿真验证。设计中reg的功能是可以选择从哪个fifo接收数据,并且可以判断fifo余量(之前是margin),