设计准备工作(设计原理图、规划项目时间)→确认原理图→新建封装(添加封装及同步)→布局工作(设置好结构、开始布局,接口、模块化)→布线工作→优化及DRC→设计资料输出→打板测试

原理图中Tools→Footprint Manager

D+U, update to PCB

按功能模块来分类→准确防止结构器件→理清信号模块分布→理清电源模块分布→放置芯片等大器件→局部模块化布局→整版进行布局优化→布局评审

同时打开原理图和PCB进行布局

1.交互选择模式下:利用AD分屏的方式把原理图和PCB同时显示在一个桌面上,方便交互式操作

2.区域内排列器件:在原理图中要选择要区分的电路,切换到PCB中进行区域内排列期间,从而达到把各个电路区分好

Tools → Cross Select Mode (Ctrl + Shift + X) 打开交互选择模式

选中原理图中器件后,进入PCB界面,Tools →Component Placement → Arrange Within Rectangle

快捷键自己设置为Alt + S

M+S(移动选择),选中要定位的器件,配合器件捕抓功能Shift+E(快捷键)

模块化能把杂乱无章的元器件快速实现分类,在布局时,多使用模块化,可以提高设计效率。

下面列出一些模块化要注意的事项:

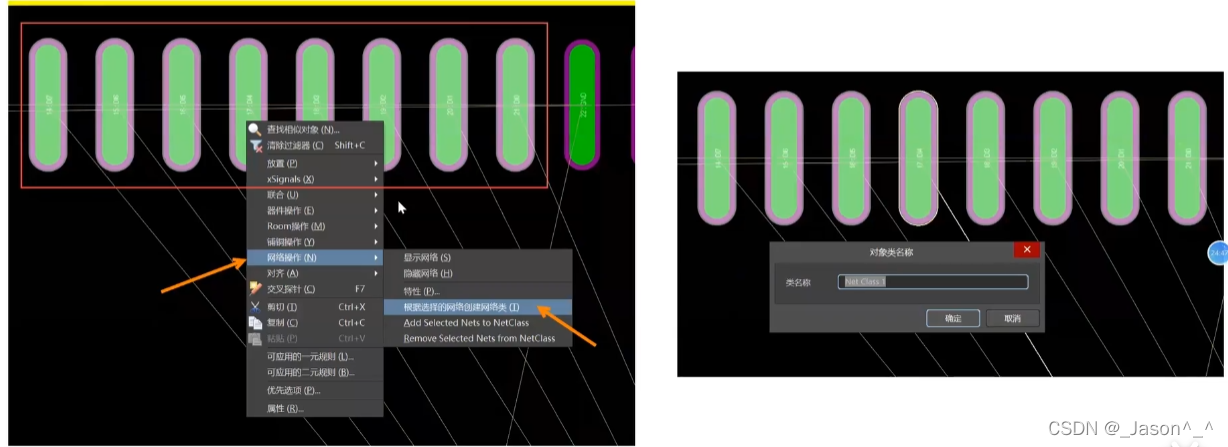

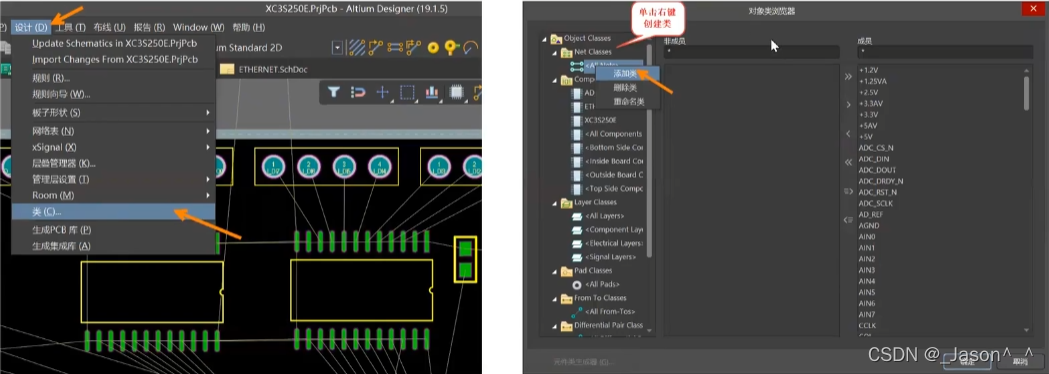

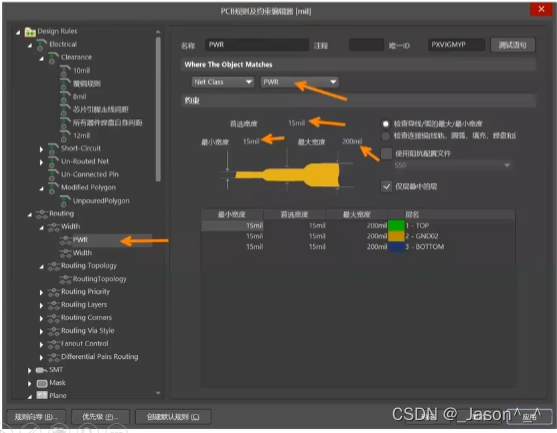

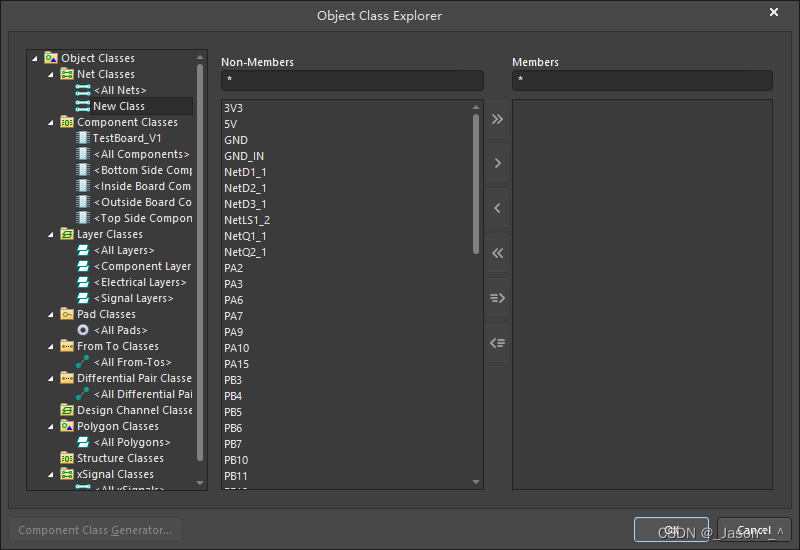

class创建及作用

打开“类管理器” Design→Classes Shortcut:DC

重点需要关注的线 需要设置类

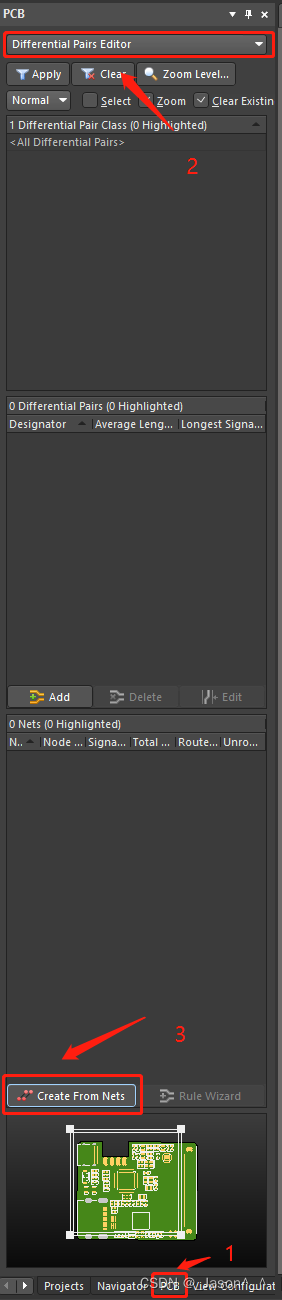

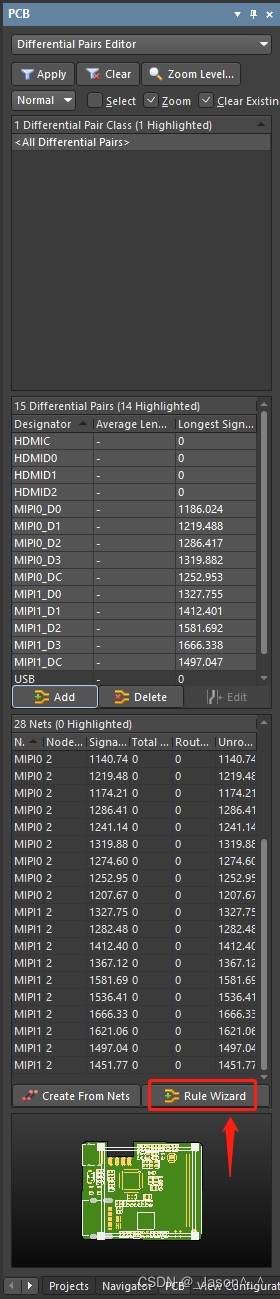

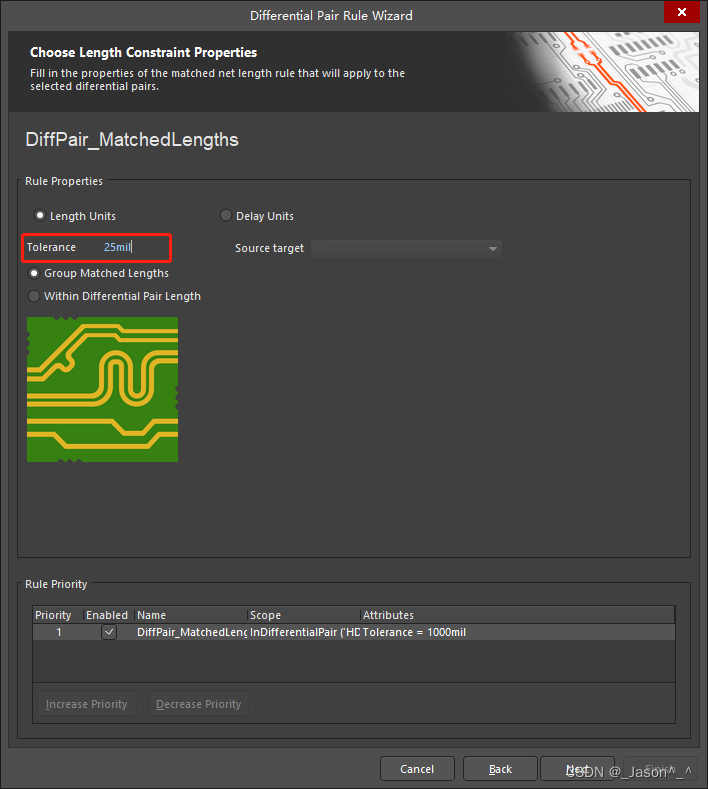

对内等长

规则:

对间等长

Route→Interactive Diff Pair Length Tuning

走线的时候可以按1234调整

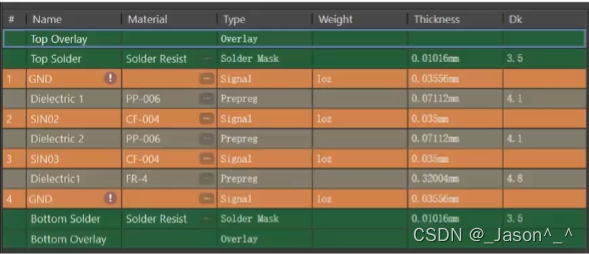

电路板的叠层安排是对PCB的整个系统设计的基础。叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要遵从两个规矩:

对此种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

对于第一种方案,通常应用于板上芯片较多的情况。这种方案可得到较好的SI性能,对于EMI性能来说并不是很好,主要通过走线及其他细节来控制。主要注意:底层放在信号最密集的信号的相连层,有利于吸收和抑制辐射;增大板面积,体现20H规则。

对于此种方案,通常应用于板上芯片密度足够低和芯片周围有足够面积(放置所要求的电源覆铜层)的场合。此种方案PCB的外层均为地层,中间两层均为信号/电源层。信号层上的电源用宽线走线,这可使电源电流的路径足控低,且信号微带路径的阻抗也低,也可同故宫外层地屏蔽内层信号辐射。从EMI控制的角度看,这是现有的最佳4层PCB结构。主要注意:中间两层信号、电源混合层的间距要拉开,走线方向垂直,避免出现串扰;适当控制板面积,体现20H规则;如果要控制走线阻抗,上述方案要非常小心的将走线布置在电源和接地铺铜的下面。另外,电源或地层上的铺铜之间应尽可能的互连在一起,以确保DC和低频的连接性。

正片:所见即所得,在正片层上走线就是将铜覆盖在你走线的地方

负片:若你在负片层走线就相当于在画线的地方把铜去掉了。

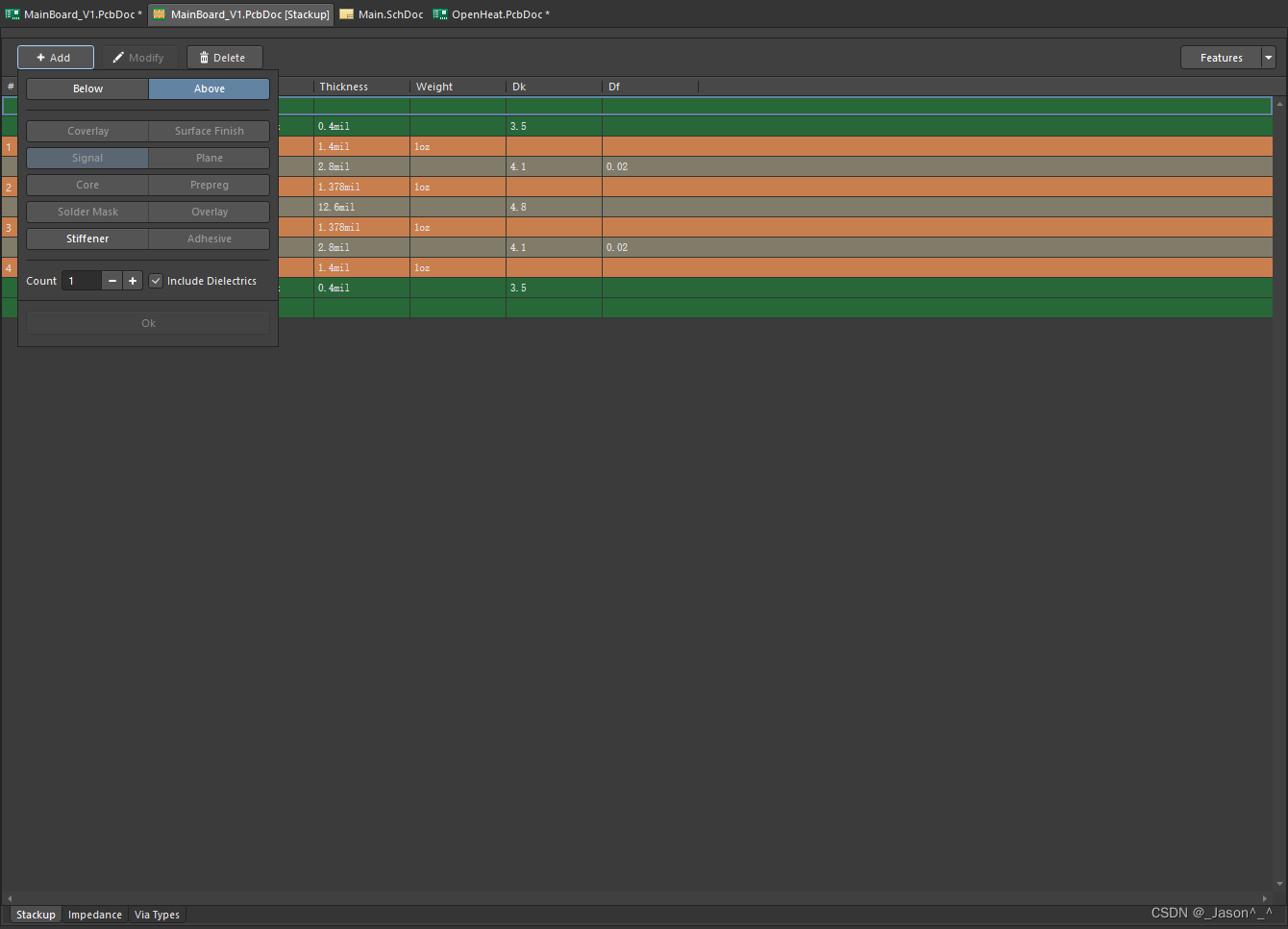

Design→Layer Stack Manager

点击ADD添加层,选择上方/下方添加

选择添加类型,signal正片层,plane负片层

对于自己画板子最好每次遵守相同的原则可以有利于养成习惯。

每个人可以有不同的习惯,我会在下面列举一些我自己的习惯。

Tools -> Annotation ->Annotate Schematics

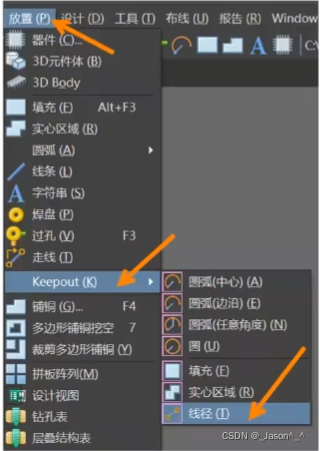

选keepout线->按Tab->Design->Board Shape->Define Board Shape From selected objects

丝印对丝印间隙约束违反

其实这些错误都是丝印层和丝印层或者是丝印层和阻焊层之间间距大小引起的问题,这是封装引起的问题,一般情况下问题不大,可以忽略,如果想去掉这个错误的话要么改封装,要么改规则设置

改Rules

在【设计规则检查】中取消这个规则的检查

打开PCB工程→打开PCB文件→点击Reports选项卡→点击Bill of Materials→选择显示属性、排序、到处文件格式→导出

Edit→Origin→Set

在3D视图下旋转PCB板 shift+鼠标右键

在bar区域,右键选择customize→toolbar选择需要工具栏

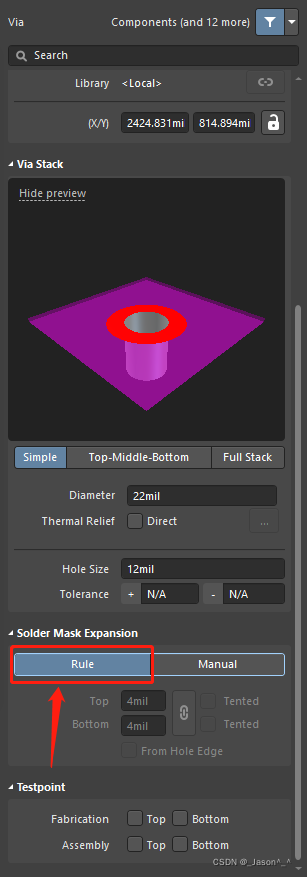

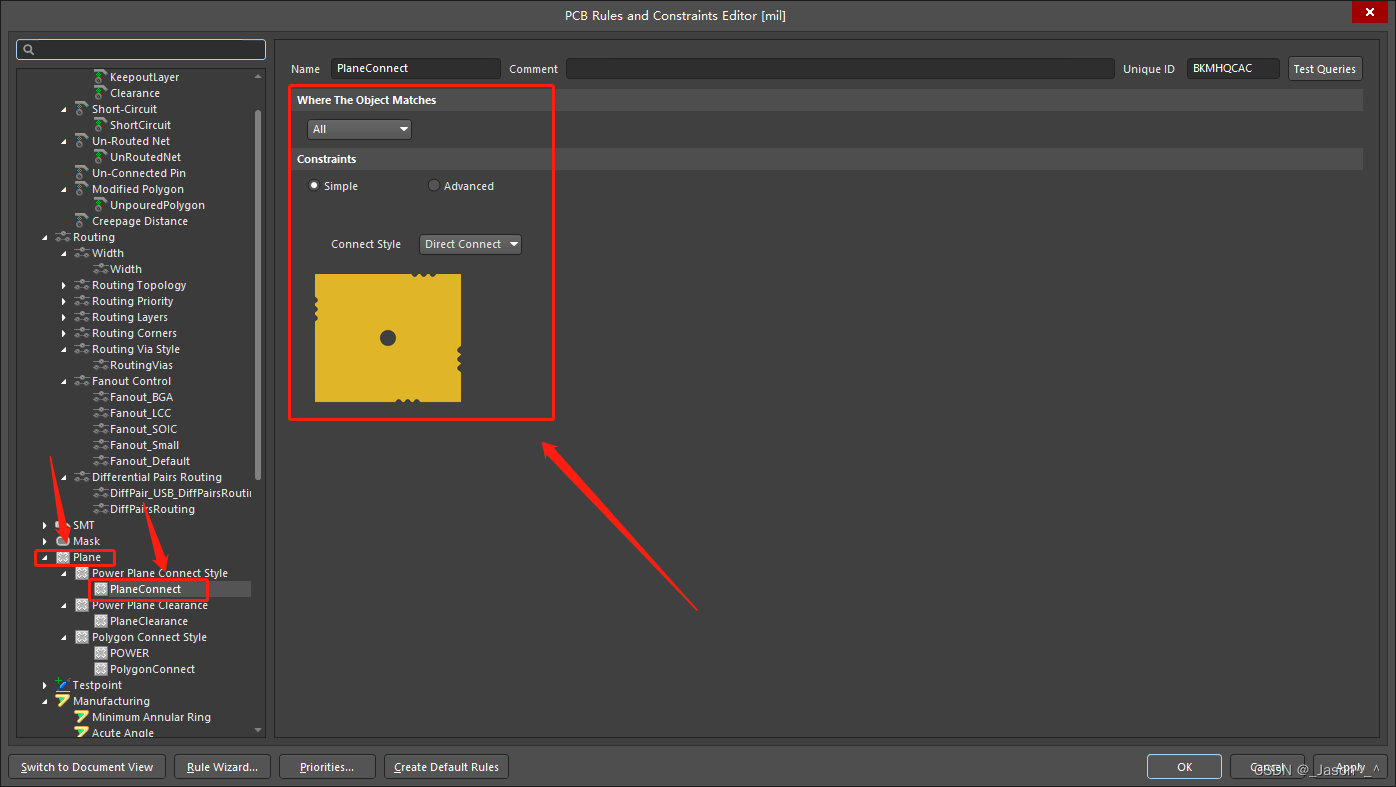

通孔、散热量大的元器件使用十字连接,如果觉得十字连接连接线太短可以更改。而如果不需要考虑散热的一般可以采用直接连接

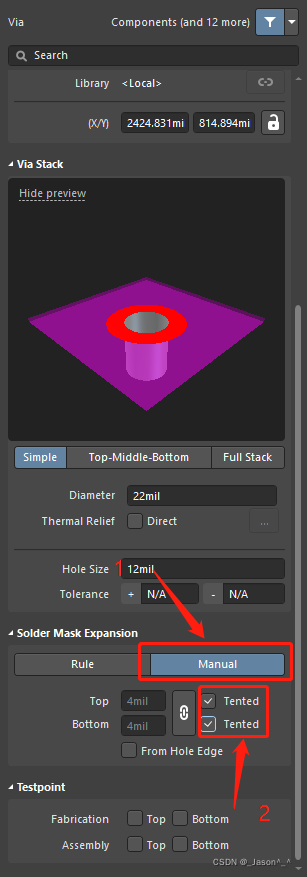

过孔开窗

过孔盖油

总的来说,勾选是盖油

不勾是开窗

若勾选了之后,再点Rule,之后的过孔默认为Manual更改之后的过孔模式

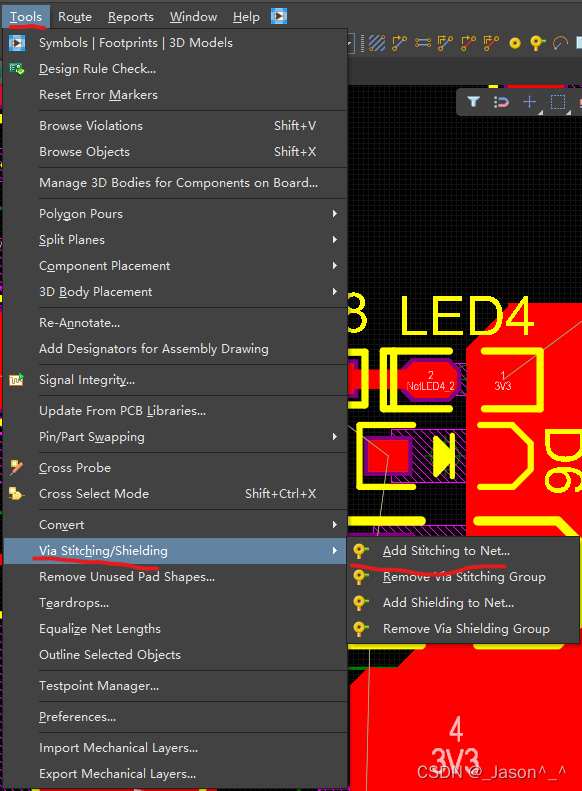

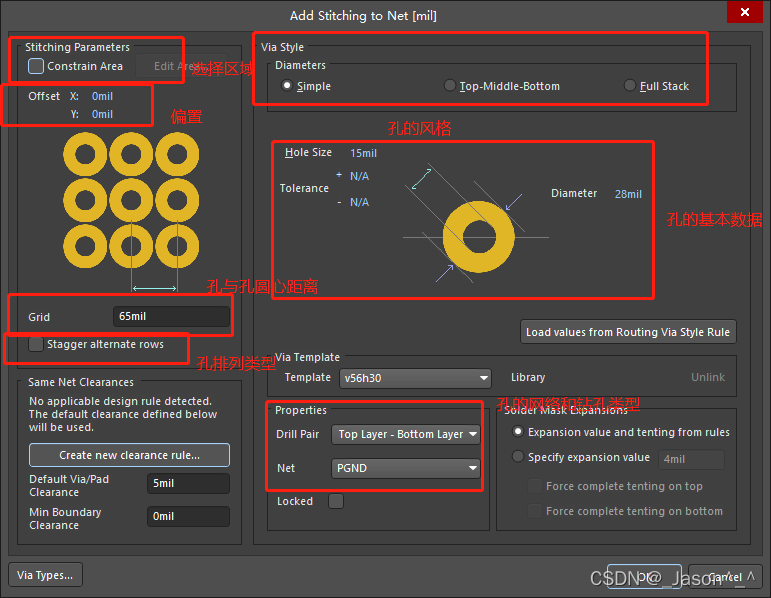

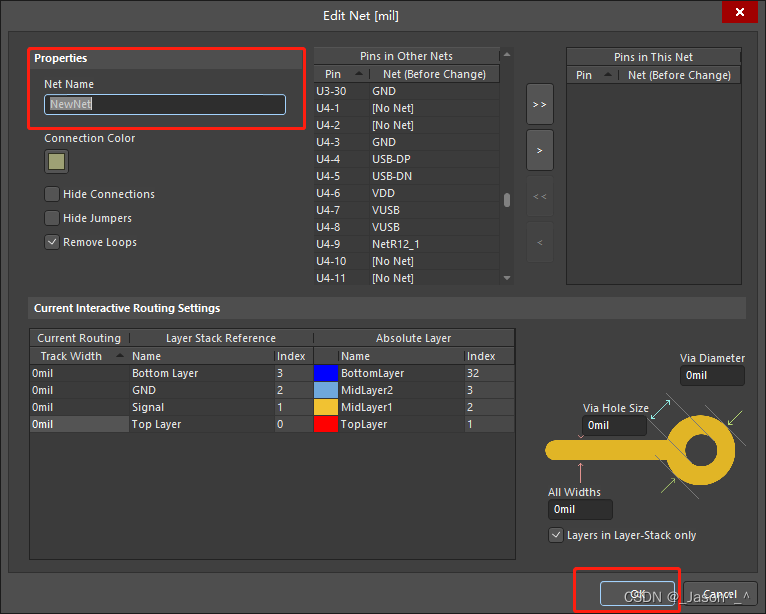

输入网络名,点击ok就可以了

按快捷键"N",Hide Connections

查找AD手册发现

检查ToolBar

在File的那一行空白处右键,Customized,Toolbars,勾选上Popups

线宽:

信号线:6mil

电源线:输入电源=一般铺铜;

过孔:holesize=10mil , diameter=18mil

| 项目 | 加工能力 | 工艺详解 |

|---|---|---|

| 钻孔孔径( 机械钻) | 0.2~6.3mm | 最小孔径0.2mm,最大孔径6.3mm,如果大于6.3mm工厂要另行处理。机械钻头规格为0.05mm为一阶,如0.2,0.3mm |

| 线宽 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

| 线隙 | 3.5mil | 多层板3.5mil 单双面板5 mil (1OZ完成铜厚),2OZ完成铜厚最小线宽线隙8mil |

| 最小过孔内径 及外径 | 内径(hole)最小0.2mm,外径(diameter)最小0.4mm | 多层板最小内径0.2mm,最小外径为0.4mm,双面板最小内径0.3mm,最小外径0.5mm |

| 焊盘边缘到线距离 | 5mil | 参数为极限值,尽量大于此参数 |

| 最小字符宽 | 线宽6mil 字符高40mil | 参数为极限值,尽量大于此参数 |

| 单片出货:走线和焊盘距板边距离 | ≥0.3mm | 否则可能涉及到板内的线路及焊盘 |

| 拼版V割出货: 走线和焊盘距板边距离 | ≥0.4mm | 否则可能涉及到板内的线路及焊盘,如右图,如果是拼版,则线离边必须要有0.4mm间距,否则v割会伤到线路。如果是单片出货,则需要≥0.2mm的间距。 |

| 最小工艺边 | 3mm | |

| 拼板:无间隙拼板 | 0mm间隙拼板 | 板子与板子的间隙为0mm。 |

| 拼板:有间隙拼板 | 1.6mm间隙拼板 | 有间隙拼版的间隙不要小于2.0mm,否则锣边时比较困难。 |

| 半孔工艺最小孔径 | 0.6mm | 半孔工艺是一种特殊工艺,最小孔径不得小于0.6mm。小于0.6MM做不出半孔的效果 |

| 阻焊层开窗 | 0.05mm | 绿油桥小于3mil不保留,绿油桥大于3mil保留,不以阻焊桥为检验出货标准,因阻焊桥不影响到性能,不接受阻焊桥客诉!阻焊桥能力:绿油桥最小3mil,其它杂色油墨最小4mil |

画线时使用此快捷键可实现捕捉功能

高亮相同网络

E+D

高亮相同网络

高亮相同网络

清除Filter

快速定义板子大小

线选

按“A”,然后选择想要的想要的排列顺序。

M+S(移动选择),选中要定位的器件,配合器件捕抓功能Shift+E(快捷键)

Shift+S

目录前言滤波电路科普主要分类实际情况单位的概念常用评价参数函数型滤波器简单分析滤波电路构成低通滤波器RC低通滤波器RL低通滤波器高通滤波器RC高通滤波器RL高通滤波器部分摘自《LC滤波器设计与制作》,侵权删。前言最近需要学习放大电路和滤波电路,但是由于只在之前做音乐频谱分析仪的时候简单了解过一点点运放,所以也是相当从零开始学习了。滤波电路科普主要分类滤波器:主要是从不同频率的成分中提取出特定频率的信号。有源滤波器:由RC元件与运算放大器组成的滤波器。可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路。无源滤波器:无源滤波器,又称

写在之前Shader变体、Shader属性定义技巧、自定义材质面板,这三个知识点任何一个单拿出来都是一套知识体系,不能一概而论,本文章目的在于将学习和实际工作中遇见的问题进行总结,类似于网络笔记之用,方便后续回顾查看,如有以偏概全、不祥不尽之处,还望海涵。1、Shader变体先看一段代码......Properties{ [KeywordEnum(on,off)]USL_USE_COL("IsUseColorMixTex?",int)=0 [Toggle(IS_RED_ON)]_IsRed("IsRed?",int)=0}......//中间省略,后续会有完整代码 #pragmamulti_c

TCL脚本语言简介•TCL(ToolCommandLanguage)是一种解释执行的脚本语言(ScriptingLanguage),它提供了通用的编程能力:支持变量、过程和控制结构;同时TCL还拥有一个功能强大的固有的核心命令集。TCL经常被用于快速原型开发,脚本编程,GUI和测试等方面。•实际上包含了两个部分:一个语言和一个库。首先,Tcl是一种简单的脚本语言,主要使用于发布命令给一些互交程序如文本编辑器、调试器和shell。由于TCL的解释器是用C\C++语言的过程库实现的,因此在某种意义上我们又可以把TCL看作C库,这个库中有丰富的用于扩展TCL命令的C\C++过程和函数,所以,Tcl是

TCP是面向连接的协议,连接的建立和释放是每一次面向连接的通信中必不可少的过程。TCP连接的管理就是使连接的建立和释放都能正常地进行。三次握手TCP连接的建立—三次握手建立TCP连接①若主机A中运行了一个客户进程,当它需要主机B的服务时,就发起TCP连接请求,并在所发送的分段中用SYN=1表示连接请求,并产生一个随机发送序号x,如果连接成功,A将以x作为其发送序号的初始值:seq=x。主机B收到A的连接请求报文,就完成了第一次握手。客户端发送SYN=1表示连接请求客户端发送一个随机发送序号x,如果连接成功,A将以x作为其发送序号的初始值:seq=x②主机B如果同意建立连接,则向主机A发送确认报

VXLAN简介定义RFC定义了VLAN扩展方案VXLAN(VirtualeXtensibleLocalAreaNetwork,虚拟扩展局域网)。VXLAN采用MACinUDP(UserDatagramProtocol)封装方式,是NVO3(NetworkVirtualizationoverLayer3)中的一种网络虚拟化技术。目的随着网络技术的发展,云计算凭借其在系统利用率高、人力/管理成本低、灵活性/可扩展性强等方面表现出的优势,已经成为目前企业IT建设的新趋势。而服务器虚拟化作为云计算的核心技术之一,得到了越来越多的应用。服务器虚拟化技术的广泛部署,极大地增加了数据中心的计算密度;同时,为

目录一、原理部分1、什么是串行通信(1)并行通信与串行通信(2)串行通信的制式(3)串行通信的主要方式 2、配置串口(1)SCON和PCON:串行口1的控制寄存器(2)SBUF:串行口数据缓冲寄存器 (3)AUXR:辅助寄存器编辑(4)ES、PS:与串行口1中断相关的寄存器(5)波特率设置 3、串口框架编写二、程序案例一、原理部分1、什么是串行通信(1)并行通信与串行通信微控制器与外部设备的数据通信,根据连线结构和传送方式的不同,可以分为两种:并行通信和串行通信。并行通信:数据的各位同时发送与接收,每个数据位使用一条导线,这种方式传输快,但是需要多条导线进行信号传输。串行通信:数据一位一

这篇文章,主要介绍如何使用SpringCloud微服务组件从0到1搭建一个微服务工程。目录一、从0到1搭建微服务工程1.1、基础环境说明(1)使用组件(2)微服务依赖1.2、搭建注册中心(1)引入依赖(2)配置文件(3)启动类1.3、搭建配置中心(1)引入依赖(2)配置文件(3)启动类1.4、搭建API网关(1)引入依赖(2)配置文件(3)启动类1.5、搭建服务提供者(1)引入依赖(2)配置文件(3)启动类1.6、搭建服务消费者(1)引入依赖(2)配置文件(3)启动类1.7、运行测试一、从0到1搭建微服务工程1.1、基础环境说明(1)使用组件这里主要是使用的SpringCloudNetflix

目录文章信息写在前面Background&MotivationMethodDCNV2DCNV3模型架构Experiment分类检测文章信息Title:InternImage:ExploringLarge-ScaleVisionFoundationModelswithDeformableConvolutionsPaperLink:https://arxiv.org/abs/2211.05778CodeLink:https://github.com/OpenGVLab/InternImage写在前面拿到文章之后先看了一眼在ImageNet1k上的结果,确实很高,超越了同等大小下的VAN、RepLK

文章目录前言一、注册小程序二、项目创建三、运行项目四、其他配置最后前言此次项目开发使用uniapp和uview进行开发,需要用到的开发工具为HBuilderX和微信开发者工具,具体的安装方式见官网,小程序注册见微信公众平台。一、注册小程序注册在微信公众平台注册小程序,按照提示注册完后会发配一个appid和密钥,需要复制保存好。完善信息设置=>基本设置,填写小程序基本信息,包括名称、头像、介绍及服务范围等。第三方设置根据开发需求添加插件授权。成员管理管理=>成员管理,点击编辑或下拉选择添加成员,输入微信号添加新的项目成员,只有成员可以进行真机测试。体验成员可以使用发布的体验版。开发设置开发=>开

ESP32学习笔记(七)复位和时钟目录:ESP32学习笔记(一)芯片型号介绍ESP32学习笔记(二)开发环境搭建VSCode+platformioESP32学习笔记(三)硬件资源介绍ESP32学习笔记(四)串口通信ESP32学习笔记(五)外部中断ESP32学习笔记(六)定时器ESP32学习笔记(七)复位和时钟1.复位2.系统时钟2.1时钟树2.2时钟源从时钟树可以看出时钟源共七种ESP32的时钟源分别来自外部晶振、内部PLL或振荡电路具体地说,这些时钟源为:2.2.1快速时钟PLL_CLK320MHz或480MHz内部PLL时钟XTL_CLK2~40MHz外部晶振时钟,模组板载的是40MHz晶